#### **CERN** CH-1211 Geneva 23 Switzerland

The Large Hadron Collider Project

## LHC Project Document No.

LHC-RFBKA-ES-000001.00 rev. 3.3

CERN Div./Group or Supplier/Contractor Document No. **AB-PO-CC**

AB-PU-CC

EDMS Document No. 349365

Date: 2002-07-29

# **Engineering Specification**

# DIAGNOSTIC INTERFACE MODULE FOR POWER CONVERTERS

#### Abstract

This document describes the physical and electrical properties of the Diagnostic Interface Module (DIM).

| Prepared by :     |

|-------------------|

| Christophe Martin |

| David Nisbet      |

| John Keith Stay   |

Checked by : André Beuret Jean-Paul Burnet Gunnar Fernqvist Quentin King Valérie Montabonnet Jean-Pierre Royer Hugues Thiesen Approved by : Frédérick Bordry

Page 2 of 32

| History of Changes                                                                  |                                                            |                                                                                                                                                         |                                                                                                                                                                                                                             |  |  |  |  |  |

|-------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Rev. No.                                                                            | Rev. No.DatePagesDescription of Changes                    |                                                                                                                                                         |                                                                                                                                                                                                                             |  |  |  |  |  |

| 0.1 draft                                                                           | 2001-10-26                                                 | 15                                                                                                                                                      | First draft for review.                                                                                                                                                                                                     |  |  |  |  |  |

| 0.2 draft                                                                           | 2001-10-30                                                 | 14                                                                                                                                                      | Second draft, minor text changes made.                                                                                                                                                                                      |  |  |  |  |  |

| 0.3 draft                                                                           | 0.3 draft 2001-10-31 14 Third draft,                       |                                                                                                                                                         |                                                                                                                                                                                                                             |  |  |  |  |  |

| 1.0 draft 2001-11-22 14 Added to EDMS                                               |                                                            |                                                                                                                                                         |                                                                                                                                                                                                                             |  |  |  |  |  |

| 2.0 draft 2002-01-23 15 New version incorporating new design ideas                  |                                                            |                                                                                                                                                         |                                                                                                                                                                                                                             |  |  |  |  |  |

| 2.1 draft 2002-07-04 24 Additional installation information included with examples. |                                                            |                                                                                                                                                         |                                                                                                                                                                                                                             |  |  |  |  |  |

| 2.2 draft 2002-07-29 24 Released version (for P/N AB-685-5091-550)                  |                                                            |                                                                                                                                                         |                                                                                                                                                                                                                             |  |  |  |  |  |

| 2.3 draft 2002-08-28 26 Interconnecting cable type specification added              |                                                            | Interconnecting cable type specification added                                                                                                          |                                                                                                                                                                                                                             |  |  |  |  |  |

| 3.0                                                                                 | 2002-11-28                                                 | <ul><li>Changed to reflect new connector type. First official releat<br/>(for P/N AB-685-5092-550).</li></ul>                                           |                                                                                                                                                                                                                             |  |  |  |  |  |

|                                                                                     |                                                            | Figures 4-2 and 4-4 corrected, SPARE1 renamed SPARE, signal direction flow clarified in Section 4.2 and <b>Table 5-8</b> , <b>Figure 4-6</b> clarified. |                                                                                                                                                                                                                             |  |  |  |  |  |

| 3.1                                                                                 | 2003-04-15                                                 | 32                                                                                                                                                      | Missing Figure 4-7 physical layout of PCB added.                                                                                                                                                                            |  |  |  |  |  |

| 3.2 draft                                                                           | Section 3 "Triggered Acquisition" updated to provide bette |                                                                                                                                                         | Correction to <b>Table 5-1</b> P/N for "Matching Connector Type.<br>Section 3 "Triggered Acquisition" updated to provide better<br>explanation of the function and timing. AMP connector Data<br>Sheet on page 32 replaced. |  |  |  |  |  |

| 3.3                                                                                 | 2003-10-20                                                 | 32                                                                                                                                                      | Additional comments from Q. King (page 8 + 28) and V.<br>Montabonnet (page 6) incorporated. <b>Figure 4-7</b> replaced<br>with Version 2.3 PCB layout. Note added to Section 1.1<br>regarding signal naming and usage.      |  |  |  |  |  |

Page 3 of 32

### **Table of Contents**

| 1.    | PURPOSE                                | 5  |

|-------|----------------------------------------|----|

| 1.1   | SUMMARY OF CHANGES                     |    |

| 1.2   | MODULE DEVELOPMENT HISTORY             | 6  |

| 2.    | SCOPE                                  | 6  |

| 3.    | DESCRIPTION                            | 7  |

| 4.    | INSTALLATION                           |    |

| 4.1   | SINGLE DIAGNOSTIC MODULE               | 10 |

| 4.2   | MULTIPLE DIAGNOSTIC INTERFACE MODULES  | 13 |

| 4.3   | TERMINATION                            | 17 |

| 4.4   | DALLAS 1-WIRE ID-BUS LOCAL NETWORK     |    |

| 4.5   | MECHANICAL                             | 19 |

| 5.    | ELECTRICAL INTERFACE                   | 21 |

| 5.1   | DIAGNOSTIC INTERFACE MODULE CONNECTORS |    |

| 5.1.1 | CONNECTOR J1                           | 22 |

| 5.1.2 | CONNECTOR J2                           | 26 |

| 5.1.3 | CONNECTOR J3                           |    |

| 5.2   | MODULE INTERCONNECTING CABLE           |    |

Page 4 of 32

## Table of Figures

| FIGURE 3-1 DIAGNOSTIC INTERFACE MODULE INSTALLATION (GENERAL)     | 7  |

|-------------------------------------------------------------------|----|

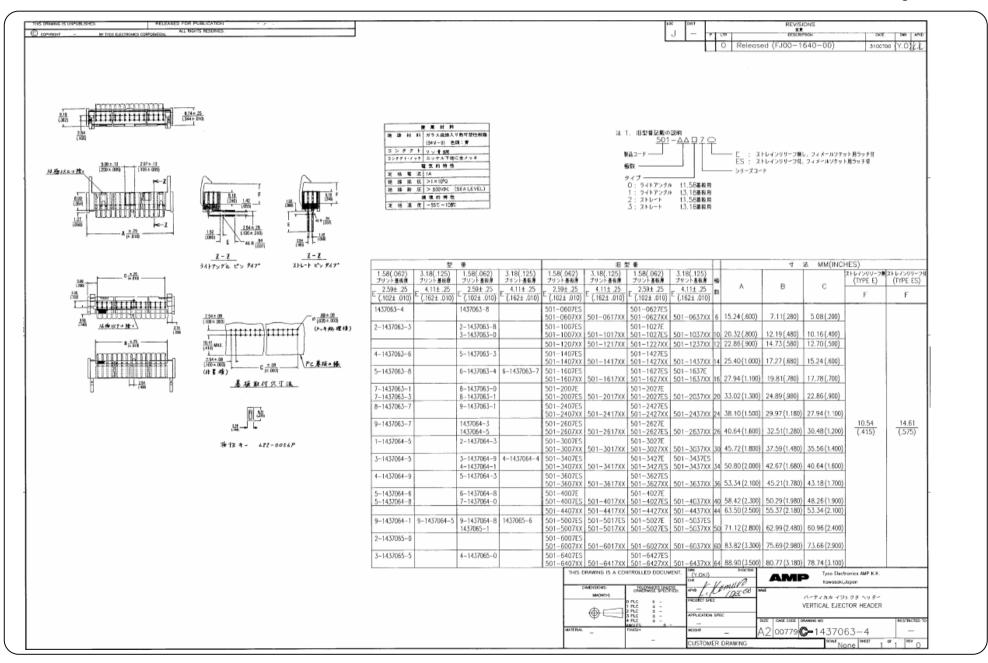

| FIGURE 4-1 SINGLE DIM MODULE INSTALLATION EXAMPLE (LAYOUT)        | 11 |

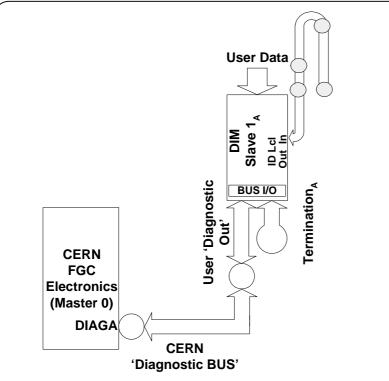

| FIGURE 4-2 SINGLE DIM MODULE INSTALLATION EXAMPLE (ELECTRICAL)    | 12 |

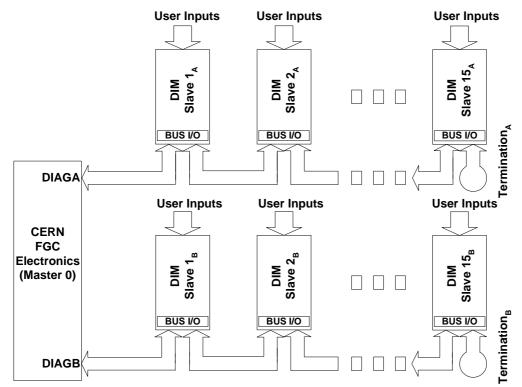

| FIGURE 4-3 MULTIPLE DIM MODULE INSTALLATION EXAMPLE (LAYOUT)      | 15 |

| FIGURE 4-4 MULTIPLE DIM MODULE INSTALLATION EXAMPLE (ELECTRICAL)  | 16 |

| FIGURE 4-5 TERMINATION DIAGRAM                                    | 17 |

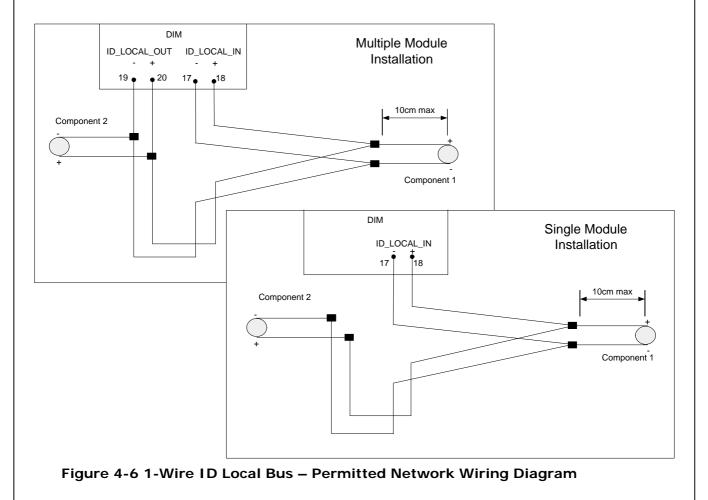

| FIGURE 4-6 1-WIRE ID LOCAL BUS – PERMITTED NETWORK WIRING DIAGRAM | 18 |

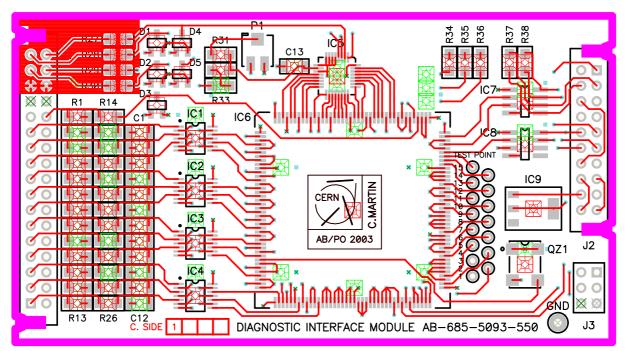

| FIGURE 4-7 DIAGNOSTIC INTERFACE MODULE: TOP SIDE LAYOUT           | 19 |

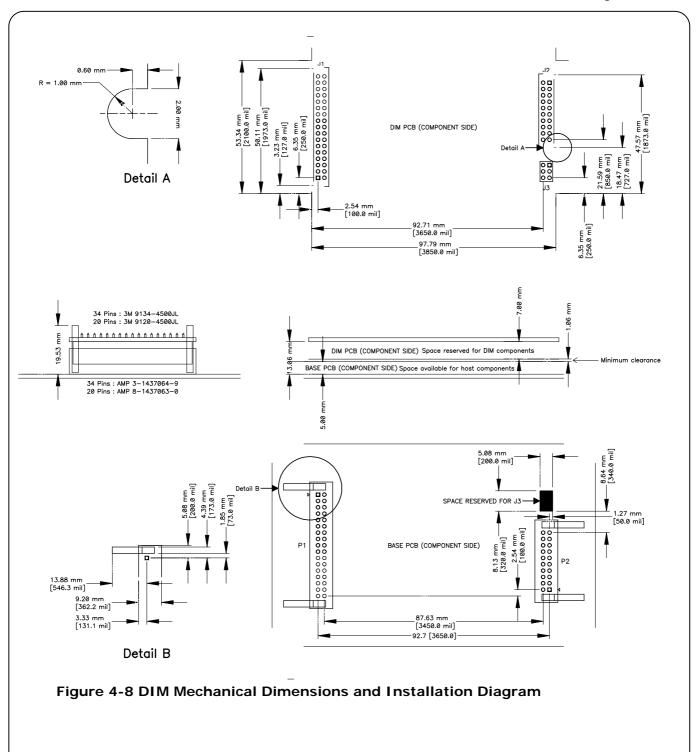

| FIGURE 4-8 DIM MECHANICAL DIMENSIONS AND INSTALLATION DIAGRAM     | 20 |

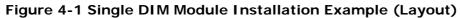

| FIGURE 5-1 TYPE AMP 3-1437064-9 HOST CONNECTOR                    | 21 |

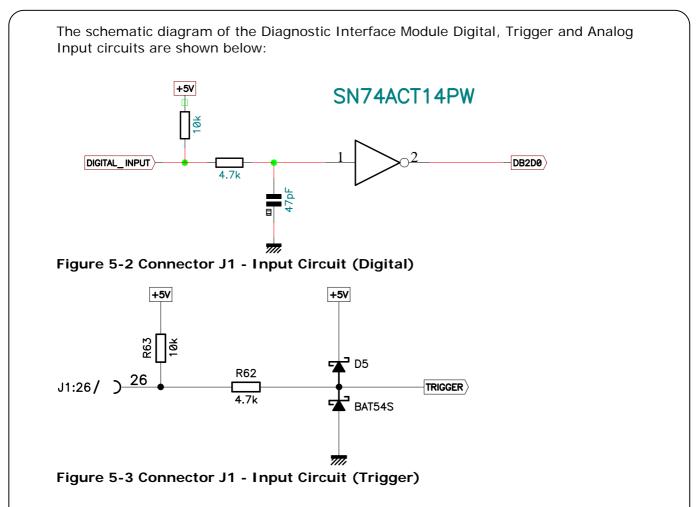

| FIGURE 5-2 CONNECTOR J1 - INPUT CIRCUIT (DIGITAL)                 | 24 |

| FIGURE 5-3 CONNECTOR J1 - INPUT CIRCUIT (TRIGGER)                 | 24 |

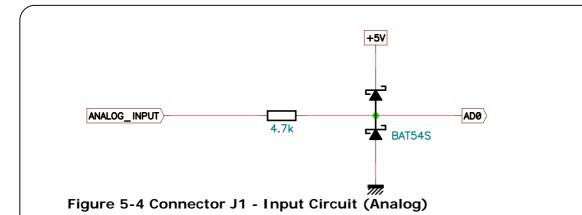

| FIGURE 5-4 CONNECTOR J1 - INPUT CIRCUIT (ANALOG)                  | 25 |

## List of Tables

| TABLE 5-1 CONNECTOR J1 - CONNECTOR TYPE              | . 22 |

|------------------------------------------------------|------|

| TABLE 5-2 CONNECTOR J1 – PIN ALLOCATION              | . 22 |

| TABLE 5-3 CONNECTOR J1 - SIGNAL DESCRIPTION          | . 23 |

| TABLE 5-4 CONNECTOR J1 – POWER SUPPLY SPECIFICATION  | . 23 |

| TABLE 5-5 CONNECTOR J1 – DIGITAL INPUT SPECIFICATION | . 24 |

| TABLE 5-6 CONNECTOR J1 – ANALOG INPUT SPECIFICATION  | . 25 |

| TABLE 5-7 CONNECTOR J2 - CONNECTOR TYPE              | . 26 |

| TABLE 5-8 CONNECTOR J2 – PIN ALLOCATION              | . 26 |

| TABLE 5-9 CONNECTOR J2 – SIGNAL DESCRIPTION          | . 27 |

| TABLE 5-10 CONNECTOR J3 - CONNECTOR TYPE             | . 28 |

| TABLE 5-11 CONNECTOR J3 – PIN ALLOCATION             | . 28 |

| TABLE 5-12 CONNECTOR J3 – SIGNAL DESCRIPTION         | . 28 |

| TABLE 5-13 INTERCONNECTING CABLE SPECIFICATION       | . 29 |

|                                                      |      |

Page 5 of 32

#### 1. PURPOSE

This document describes the physical and electrical properties of the **D**iagnostic Interface **M**odule (DIM) for Power Converters.

The module has been developed for the remote collection of digital and analog information by the Function Generator Controller (FGC) developed by the AB-PO-CC section. While the data source will normally be a power converter, other external equipment may also interface to the system.

#### Warning

The Diagnostic Interface Module shall under no circumstances be inserted or removed from the host equipment when this is under power. Failure to observe this warning may result in damage to or destruction of the module.

#### **1.1 SUMMARY OF CHANGES**

Please note that previous versions of this document and of the hardware described a different type of connector for mating the DIM to its host. The latest document (from Rev. 3.2 onwards) specifies connectors with an integrated extraction mechanism. This change is electrically transparent to the user as the host connector positions and pin-out remains identical. However, the new connectors facilitate easier insertion and removal of the module from its host equipment.

#### Some other small changes have also been implemented and are listed below:

change for users in the DIM physical size and height clearance requirement above the host, which are now as follows (see Figure 4-8):

| Old dimensions $L = 99.10$ mm | W = 47.00 mm | Height = 17.0mm |

|-------------------------------|--------------|-----------------|

| New dimensions $L = 97.79mm$  | W = 53.34mm  | Height = 20.0mm |

- DIAGNOSTIC\_SPARE+/- and DIAGNOSTIC\_DATA+/- pairs were shorted at the termination. The DIAGNOSTIC\_SPARE+/- shall now be looped back to the DIAGNOSTIC\_DATA+/- inputs respectively, as shown in Section 4.

- The Digital Input Specification in **Table 5-5** has been modified to show the Sink Current Requirement rather than Input Impedance and the TRIGGER Rise Time requirement has been added.

**Note:-**The pin connections labelled with the name "SPARE", or including the word "SPARE" are **reserved** for CERN test purposes and or future development and shall not be used for any other purpose in the host equipment.

Using these pins, the loop back installed at the last module in the daisy chain as specified in Section 4.3, allows a continuity check to be carried out of the serial data bus.

Page 6 of 32

#### **1.2 MODULE DEVELOPMENT HISTORY**

The development hardware module has been designed by the AB-PO-CC section and carries the following designation:

AB-685-5091-550

A pre-production hardware version carries the following designation: AB-685-5092-550

The final hardware version for series production will carry the designation: AB-685-5093-550

The latter designation will also change to the use of the LHC Equipment Identification code for this final version (HCRFBKA\_\_\_\_).

This specification is valid for all of the above versions except as noted in Section 1.1.

#### 2. SCOPE

The purpose of the document is to provide sufficient information to a CERN or Industry user, to facilitate the physical and electrical incorporation of one or more of the Diagnostic Interface Modules into their design.

#### 3. DESCRIPTION

The Diagnostic Interface Module (DIM) is designed for installation in any equipment, for the remote collection of digital and analog information. The module is powered by the user equipment in which it is installed. There are no control functions or hand-shake requirements for the acquisition of data.

Each module functions as a slave device, connected to a serial diagnostic data bus that is controlled by a master device. Each bus may have any number of diagnostic modules (to a maximum of 15) connected in a "daisy-chain". One or two buses are available depending on the user requirements.

Figure 3-1 Diagnostic Interface Module Installation (General)

All data buses used, shall be correctly terminated (see installation instructions). An unused bus does not require termination.

The Master Module is interfaced internally in the CERN FGC Electronics with the Queued Serial Module (QSM) peripheral infrastructure of the Motorola MC68HC16Z1 microcontroller (HC16).

Three LED's on the back of the module indicate POWER, CLK and TRIG (memorised).

The module may acquire user data using the following acquisition channels:

- Analog (4 inputs)

- Digital (24 inputs)

- Trigger (1 input)

- DALLAS 1-Wire® ID-bus local network (1 Input, 1 Output)

#### Acquisition

All analog and digital data from all diagnostic modules are acquired by the CERN Function Generator Controller (FGC) Electronics every 20ms. Sampling at this frequency implies a maximum signal bandwidth of 25Hz, thus all analog inputs should be filtered below this frequency to prevent aliasing effects.

#### Analog Inputs

The 4 analog inputs interface to a 12-bit Analog Digital Converter (ADC) that connects to the controller for subsequent data serialisation. Total accuracy with temperature and linearity effects is specified as 10 bits.

A 2.5V reference voltage used by the ADC is also available to the host device. As a series resistor protects this output, the 2.5V reference should be buffered before use.

#### **Digital Inputs**

Each of the 24 digital input bits are pulled up to +5V at the input, filtered with an R-C network and then buffered before serialisation by the controller CPLD.

#### **Triggered Acquisition**

A Trigger input is provided for latching the status of the digital inputs DIN00 to DIN23 for fault diagnosis. This allows for determination of which signal initially causes a Fault/Alarm condition. Activation of the trigger stops an internal clock that is subsequently processed by the CERN FGC Electronics, to provide a 1<sup>st</sup> Fault analysis to a resolution of 8µs.

Analog data acquisition by the DIM is unaffected by the Trigger input.

The latching of the digital inputs, occurs 1µs after the receipt of the '+'ve edge transition on the Trigger signal input, allowing for any circuit delays present and de-bouncing of the DIN inputs. The maximum delay between the assertion of the Trigger signal and the assertion of the relevant DIN bits shall be <500ns. The latched inputs will be reset by the DIM controller CPLD once the values have been correctly read out to the FGC.

Following a trigger event, all digital inputs will only return to the normal free-running mode after the reset command has been sent by the FGC – this will normally occur within 100ms. This allows for an immediate return to valid diagnostic data acquisition of the DIN inputs by the DIM, even if the Trigger input has not been reset to "0" by the user, which must occur before any further 1<sup>st</sup> Fault data can be acquired.

#### DALLAS 1-Wire® ID Bus Local Network Acquisition

The ID Bus is a network of parallel-connected devices self-powered from the data line and hence may function when the user equipment is not powered. Each device is pre-programmed with a unique identity number

The ID Local bus is an extension of the ID Bus and is used to identify functional units within the user equipment, generally those that may be easily removed. Once in operation, a list of connected units will be automatically generated at regular intervals. With the aid of database systems this information will be a powerful tool for subsequent inventory management.

The following Dallas (now Maxim) semiconductor devices may be connected to a Diagnostic Interface Module ID Local Bus:

DS2401 TO92 64bit identity tag

Page 9 of 32

DS2401Z SOT223 64bit identity tag

While the ID Local Bus operates without power, certain guidelines and constraints apply to the installation (see the following installation chapter of this document).

Page 10 of 32

#### 4. INSTALLATION

#### 4.1 SINGLE DIAGNOSTIC MODULE

The information below is valid for systems using only a single Diagnostic Interface Module regardless of ID Local Bus parameters.

Connector J1 (see Section 5 Electrical interface)

- Section 5.1.1 describes the connector analog and digital inputs.

- The equipment 'Sum of faults' generated by the host will normally generate the Trigger.

- Analog inputs should be buffered with a low impedance, current limited voltage source.

- The user may choose to use the Vref output (buffered) when performing a level shift of bipolar analog signals (alternatively an external Vref may be used).

- The user should connect all unused analog and digital inputs to OV.

- The user should provide the +5V module supply via this connector (see **Table 5-4**).

#### Connector J2 (see Section 5 Electrical interface)

- The DATA\_OUT, CLK\_IN, SPARE\_IN and ID\_OUT pins should be connected to the CERN FGC Electronics DIAGA or DIAGB diagnostic connector. The CERN FGC Electronics connector is defined in the document 'LHC Function Generator Controller Electronics Installation - Interface Specification', EDMS Nr. 339391.

- The DATA\_IN, CLK\_OUT, SPARE\_OUT and ID\_IN pins should be terminated according to the data given in Section 4.3 of this chapter. The termination will normally be made on the circuit board where the Diagnostic Interface Module is installed.

- The 'ID Local In' pins should be connected to the user ID Local Bus components following the recommendations in the 'ID Local Bus' section of this chapter. Note that as no further diagnostic modules will be connected in this installation, closing the 'ID Local Bus' loop is not required.

- The 'ID Local Out' pins should be left unconnected.

#### Single Module Installation Example

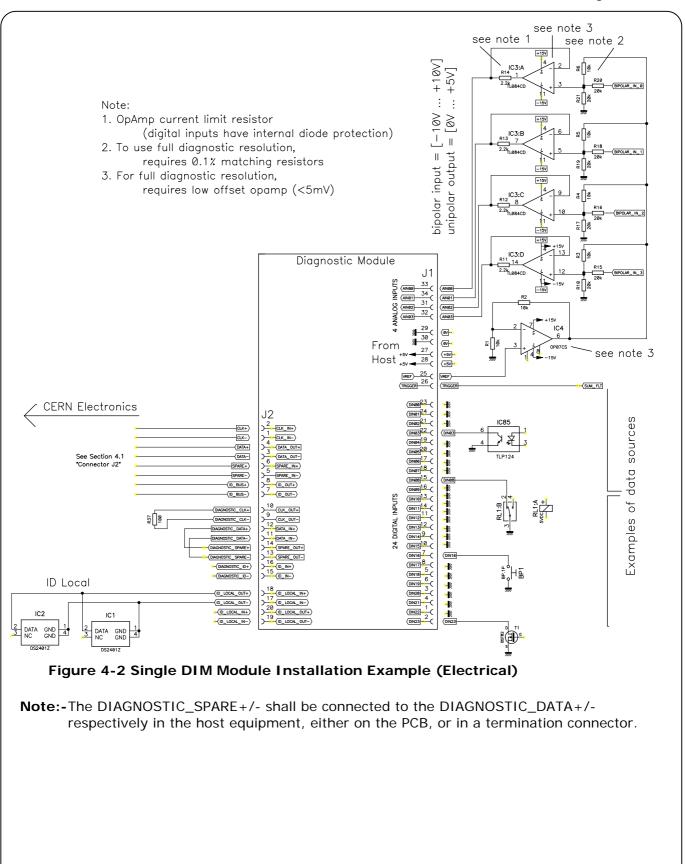

An example of a single diagnostic module installation is shown below. Figure 4-1 shows the connectivity to the CERN FGC Electronics. Figure 4-2 shows a small ID-bus connection with two components attached, 4 bipolar  $\pm 10V$  analog inputs using the on board reference and some examples of actuation devices attached to the Digital Inputs.

The total number of ID components that can be connected shall be <100.

Note that should a high precision analog measurement be required, this example requires the use of low offset op-amps (<5mV) and high precision resistors (0.1%).

#### LHC Project Document No. LHC-RFBKA-ES-000001.00 rev. 3.2

Page 11 of 32

Page 12 of 32

Page 13 of 32

#### 4.2 MULTIPLE DIAGNOSTIC INTERFACE MODULES

The information below is valid for all systems using more than one Diagnostic Interface Module (DIM).

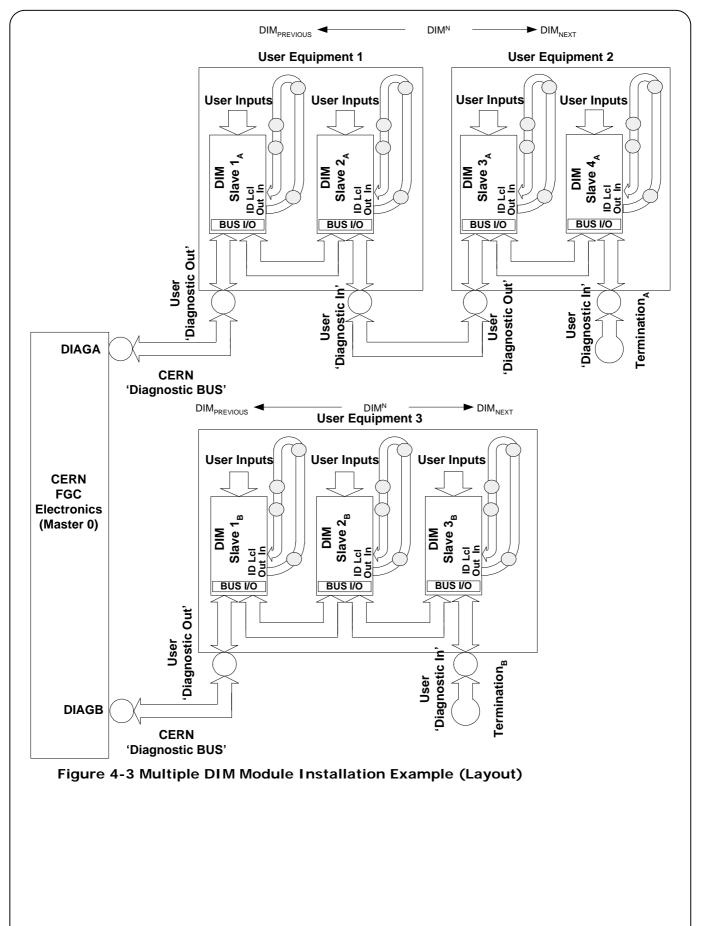

For clarification the term " $DIM_{PREVIOUS}$ " refers either to the "Master DIMO' in the FGC or to the next DIM module in the direction **towards** the FGC. The term " $DIM_{NEXT}$ " refers to the first or subsequent DIM modules in the direction **away** from the FGC, as shown in **Figure 4-3**.

#### General

- No more than 15 modules may be connected on a single bus.

- Modules may be connected together via a cable or by circuit board layout.

- Cable length:

- Total length from the CERN FGC Electronics to the furthermost module, not including the ID\_local\_bus, shall not exceed 100m (measured along the signal path).

- Total length from the CERN FGC Electronics to the furthermost module, including the ID\_local\_bus, shall not exceed 100m (measured along the signal path).

- The total number of ID components that can be connected shall be <100.

#### Connector J1 (see Section 5)

• See Section 4.1: Single Module for J1 installation guidelines.

#### Connector J2 (see Section 5)

- The DIM module DATA\_OUT, CLK\_IN, SPARE\_IN and ID\_OUT pins should be connected to the DIM<sub>PREVIOUS</sub> module DATA\_IN, CLK\_OUT, SPARE\_OUT and ID\_IN, OR to the CERN FGC Electronics DIAGA or DIAGB diagnostic connector.

- The CERN FGC Electronics DIAGA/B connector is defined in the document 'LHC Function Generator Controller Electronics Installation - Interface Specification', EDMS Nr. 339391.

- If the DIM is to connect to a DIM<sub>NEXT</sub> module located in the same equipment, this connection will normally be made on the circuit board where the module is installed.

- If the DIM is to connect to a DIM<sub>NEXT</sub> module located outside of the equipment, the relevant equipment Technical Specification will specify the connector to be used.

- The DIM module DATA\_IN, CLK\_OUT, SPARE\_OUT and ID\_IN pins should be connected to the DIM<sub>NEXT</sub> module DATA\_OUT, CLK\_IN, SPARE\_IN and ID\_OUT pins, or terminated according to the data given in Section 4.3 of this chapter.

- If the DIM is to connect to a DIM<sub>PREVIOUS</sub> module located in the same equipment, this connection will normally be made on the circuit board where the module is installed.

- If the DIM is to connect to a DIM<sub>PREVIOUS</sub> module located outside of the equipment, the relevant equipment Technical Specification will specify the connector to be used.

- The 'ID Local In' pins should be connected to the user ID Local Bus following the recommendations in the 'ID Local Bus' section of this chapter. Should the user not require an 'ID Local Bus', the 'ID Local In' pins shall be connected directly to the 'ID Local Out' pins, thus assuring the ID Bus continuity.

- The 'ID Local Out' pins should be connected to the user ID Local Bus following the recommendations in the 'ID Local Bus' section of this chapter.

#### Multiple Diagnostic Interface Module Installation Example

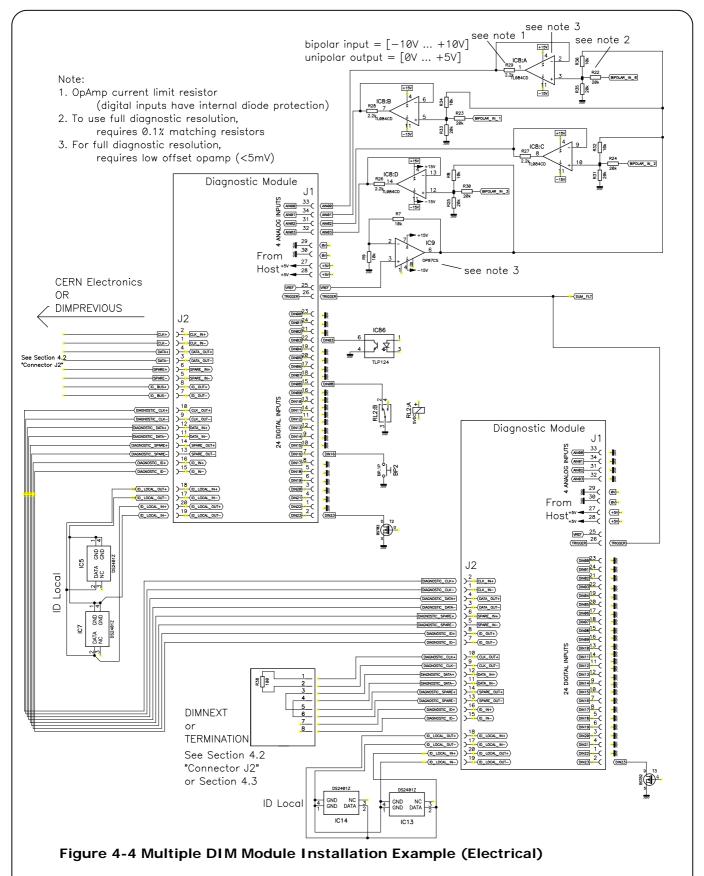

An example of a multiple DIM module installation is shown below. **Figure 4-3** shows one possible way of connecting 7 modules to the CERN FGC Electronics. **Figure 4-4** shows two modules as they could be connected on a circuit board as part of a multiple DIM module installation.

The first DIM module possesses a Local ID-bus connection, 4 bipolar  $\pm 10V$  analog inputs using the on board reference and some examples of actuation devices. Note that should a high precision analog measurement be required, this example requires use of low offset op-amps (<5mV) and high precision resistors (0.1%).

The second DIM module has no analog input and only 1 digital input and uses the same trigger as the first module. If this is the last module then a terminating connector should be fitted.

LHC Project Document No. LHC-RFBKA-ES-000001.00 rev. 3.2

Page 15 of 32

#### Page 16 of 32

**Note:-**The DIAGNOSTIC\_SPARE+/- shall be connected to the DIAGNOSTIC\_DATA+/- respectively in the host equipment, either on the PCB, or in the termination connector.

Page 17 of 32

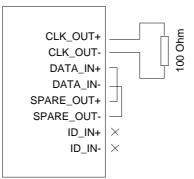

#### 4.3 TERMINATION

The last module on any DIM bus should be terminated as follows:

#### Figure 4-5 Termination Diagram

Termination may be made either:

- on the circuit board where the DIM module is mounted, particularly in the case of a single module installation.

- with a terminating connector, particularly in the case of modular installations where several identical equipments may be connected within the user system

- **Note:-**The DIAGNOSTIC\_SPARE+/- shall be connected to the DIAGNOSTIC\_DATA+/- respectively in the host equipment, either on the PCB, or in the termination connector.

#### 4.4 DALLAS 1-WIRE ID-BUS LOCAL NETWORK

The 1-Wire ID bus is a part-digital part-analog identification system that exploits variations in system (cable) capacitance, in conjunction with a 9600baud communication protocol, to read all devices found on the bus. Due to the method of operation, the 1-Wire ID Bus is particularly sensitive to network layout and cable capacitance. These are addressed in the notes below.

The 1-Wire ID Bus will generally not be operating when the user equipment is functioning, thus minimising the risk of interference between systems. Operation will be activated by the CERN FGC Electronics only when conditions are acceptable to do so. However, when the user equipment is in standby, there may be signals within the user equipment that could affect the 1-Wire ID Bus signal integrity. For this reason, care should be taken not to route high frequency signals (e.g. system clocks or inverter gate drives) alongside the 1-Wire ID Data Bus, except where these signals are inactive during equipment standby.

Before considering the system further, the 'network weight' must first be understood. Network weight is the given by:

$$W = L + \left(\frac{x}{2}\right)$$

where

L = total network cable length (in metres)

x = total number of ID components on the network

Page 18 of 32

User equipment is considered 'light weight' where W<30. All other users are considered 'heavy weight'.

As with most data lines, impedance mismatching and poor network layout will cause reflections, with a high probability of data corruption. In addition, the 1-Wire ID Bus operation is sensitive to bus capacitance, more so as the bus weight increases. To minimise problems due to these effects the following guidelines are given:

- All 1-Wire ID Data Buses shall be wired in a serial chain (see **Figure 4-6** below). Star connections are forbidden.

- Branches from the 1-Wire ID Data Bus shall be limited to 10cm maximum (see Figure 4-6 below).

- Light weight users (W < 30): internal to the user equipment cable capacitance is considered to be insignificant and is thus not specified. However, cable impedance shall be 100Ω ±20%. External to the user equipment a standardised data cable type shall be used (see Section 5.2).</li>

- Heavy weight users (W>30): a standardised data cable type shall be used throughout (see Section 5.2).

- Where a circuit board is used to route the 1-Wire ID Local Bus, care should be taken to not create a star configuration network but to route as shown in the figure below.

Page 19 of 32

#### 4.5 MECHANICAL

The top (connector) side of the module (Version 2.3) is shown in the **Figure 4-7** below.

Figure 4-7 Diagnostic Interface Module: Top side layout

The module is constructed as a multi-layer printed circuit board with components mainly mounted on the top side. There are a small number of surface mount decoupling resistors, capacitors and LEDs mounted on the bottom side. The overall module dimensions are 97.79mm x 53.34mm (see **Figure 4-8**).

Located at each end, on the main components side, are the user input/output, CERN input/output and JTAG connectors (J1, J2 and J3 respectively). The JTAG connector J3 is intended solely for use by CERN authorised persons once the module has been removed from the user equipment.

The module is installed as a daughter-board, attached in a piggyback fashion to a larger motherboard. Use of the motherboard area directly below the diagnostic module is permitted, however maximum component height limitations apply (refer to **Figure 4-8** below for physical installation description). Note that the CPLD IC6 (located approximately in the centre of the module), generates some heat and thus the placement of sensitive components facing this location should be avoided.

Due regard should be taken on the host equipment in the areas where the DIM module retaining catches rotate down when extracting the module (see **Figure 4-8**).

# LHC Project Document No.

Page 20 of 32

Page 21 of 32

### 5. ELECTRICAL INTERFACE

#### 5.1 DIAGNOSTIC INTERFACE MODULE CONNECTORS

The connector types specified in the **Table 5-1** and **Table 5-7** provide a simple but effective means for both the mechanical locking in-place and for easy extraction of the DIM modules from their host equipment. The following image shows the 34 pin host side type.

#### Figure 5-1 Type AMP 3-1437064-9 Host Connector

The data sheet for the required mating connector type in the host equipment can be seen on Page 32 of this document. The WWW site url is:

http://ecommas.tycoelectronics.com/commerce/DocumentDelivery/DDEController?Action= ecatdrawselcritrslt&Part=1437063-4

The electrical characteristics of the signal interfaces to the module at J1, and J2 are given in the following section

Page 22 of 32

#### 5.1.1 CONNECTOR J1

#### 5.1.1.1 CONNECTOR TYPE

| Connector No. | Module Connector<br>Supplier/Type | Matching Connector<br>Supplier/Type |  |  |

|---------------|-----------------------------------|-------------------------------------|--|--|

| J1            | 3M 9134-4500JL                    | AMP 3-1437064-9 - (See Page 32)     |  |  |

#### Table 5-1 Connector J1 - Connector type

The connector J1 located on the DIM module provides all of the interconnection with the host equipment for the digital, analog and power signals as listed below.

#### 5.1.1.2 PIN ALLOCATION

| J1 Pin number                 | Signal name                              |

|-------------------------------|------------------------------------------|

| 33, 34, 31, 32                | AIN00 to AIN03 respectively              |

| 29, 30                        | OV Ground from host                      |

| 27, 28,                       | +5V Power from host                      |

| 25                            | VREF (External Reference Voltage Output) |

| 26                            | TRIGGER (1 <sup>ST</sup> FAULT)          |

| 23, 24, 21, 22, 19, 20, 17,   | DIN00 to DIN11 respectively              |

| 18, 15, 16, 13, 14            |                                          |

| 11, 12, 9, 10, 7, 8, 5, 6, 3, | DIN12 to DIN23 respectively              |

| 4, 1, 2                       |                                          |

#### Table 5-2 Connector J1 – Pin allocation

#### LHC Project Document No. LHC-RFBKA-ES-000001.00 rev. 3.2

Page 23 of 32

#### 5.1.1.3 SIGNAL DESCRIPTION

| Name              | Source/<br>Destin. | Source<br>Type<br>OC=Open<br>Collector | Parameter                               | Function                                                                                               |

|-------------------|--------------------|----------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------|

| DINOO to<br>DIN23 | User / DIM         | OC Output                              | Hi = [2.0VVcc]<br>Lo = [0V 0.8V]        | DIM module Digital Inputs.                                                                             |

| TRIGGER           | User / DIM         | OC Output                              | Hi = [2.0VVcc]<br>Lo = [0V 0.8V]        | Latching of DIN00-DIN23 in<br>the DIM module occurs on the<br>positive going edge of this<br>signal    |

| AIN00 to AIN03    | User / DIM         | Analog<br>Output                       | 0 to +5V                                | DIM module Analog Inputs 0-<br>3 (non-latched).                                                        |

| VREF              | DIM / User         | Analog<br>Output                       | +2.50 VDC<br>Z <sub>OUT</sub> = 1k Ohm. | Reference Voltage (2.5V)<br>used by the DIM module ADC<br>and made available to the<br>user equipment. |

|                   |                    |                                        |                                         | If used, it shall be adequately<br>buffered in the host<br>equipment                                   |

| POWER (Vcc)       | User / DIM         | +5V<br>±0.25V<br>Input                 | <200 mA                                 | Power to the DIM module from the host equipment.                                                       |

| POWER GND         | User / DIM         | OV                                     |                                         | Power return/Ground<br>reference to DIM module from<br>the host                                        |

Table 5-3 Connector J1 - Signal Description

| Parameter           | Min. | Typical | Max. | Unit |

|---------------------|------|---------|------|------|

| Power               |      |         |      |      |

| Supply +Vcc         | 4.75 | 5       | 5.25 | Volt |

| Current Consumption | -    | <200    | -    | mA   |

Table 5-4 Connector J1 – Power Supply Specification

Page 24 of 32

| Parameter                | Min. | Typical | Max.      | Unit |

|--------------------------|------|---------|-----------|------|

| Digital/Trigger Inputs   |      |         |           |      |

| Absolute maximum input   | -0.3 |         | Vcc + 0.3 | Volt |

| High Level Threshold     | 2.0  | -       | -         | Volt |

| Low Level Threshold      | -    | -       | 0.8       | Volt |

| Sink Current Requirement | 1    | -       | -         | mA   |

| Trigger Input            |      |         |           |      |

| Rise Time (0.8 to 2.0V)  | -    | -       | 40        | nS   |

Table 5-5 Connector J1 – Digital Input Specification

#### LHC Project Document No. LHC-RFBKA-ES-000001.00 rev. 3.2

Page 25 of 32

| Parameter              | Min. | Typical     | Max.       | Unit |

|------------------------|------|-------------|------------|------|

| Analog Inputs          |      |             |            |      |

| Absolute maximum input | -0.3 |             | Vcc + 0.3V | Volt |

| Input Voltage Range    | 0    |             | +5         | Volt |

| Input Impedance        | -    | 5MΩ // 15pF | -          | Ohm  |

Table 5-6 Connector J1 – Analog Input Specification

LHC Project Document No.

Page 26 of 32

#### 5.1.2 CONNECTOR J2

#### 5.1.2.1 CONNECTOR TYPE

| Connector No. Module Connector<br>Supplier/Type |                | Matching Connector<br>Supplier/Type |  |  |  |

|-------------------------------------------------|----------------|-------------------------------------|--|--|--|

| J2                                              | 3M 9120-4500JL | AMP 8-1437063-0 - (See Page 32)     |  |  |  |

Table 5-7 Connector J2 - Connector type

#### 5.1.2.2 PIN ALLOCATION

| J2 Pin number | Signal name   | Connection Direction<br>(see Section 4.2) |

|---------------|---------------|-------------------------------------------|

| 1             | CLK_IN-       |                                           |

| 2             | CLK_IN+       |                                           |

| 3             | DATA_OUT-     |                                           |

| 4             | DATA_OUT+     | DIM                                       |

| 5             | SPARE_IN-     |                                           |

| 6             | SPARE_IN+     |                                           |

| 7             | ID_OUT-       |                                           |

| 8             | ID_OUT+       |                                           |

| 9             | CLK_OUT-      |                                           |

| 10            | CLK_OUT+      |                                           |

| 11            | DATA_IN-      |                                           |

| 12            | DATA_IN+      | DIM                                       |

| 13            | SPARE_OUT-    | DIM <sub>NEXT</sub>                       |

| 14            | SPARE_OUT+    |                                           |

| 15            | ID_IN-        |                                           |

| 16            | ID_IN+        |                                           |

| 17            | ID_LOCAL_IN-  |                                           |

| 18            | ID_LOCAL_IN+  | TO/FROM Local                             |

| 19            | ID_LOCAL_OUT- | DALLAS ID Devices                         |

| 20            | ID_LOCAL_OUT+ |                                           |

Table 5-8 Connector J2 – Pin Allocation

Page 27 of 32

### 5.1.2.3 SIGNAL DESCRIPTION

All signals are differential pairs.

| Name                | Source/<br>Destin.                            | Source<br>Type | Function                                   |

|---------------------|-----------------------------------------------|----------------|--------------------------------------------|

| CLK_OUT±<br>CLK_IN± | CERN FGC<br>Electronics /<br>DIM <sub>n</sub> | RS485          | Parallel 500kHz clock for serialising data |

| DATA_IN±            | DIM <sub>n-1</sub> / DIM <sub>n</sub>         | RS485          | Serial data from preceding DIM module      |

| DATA_OUT±           | DIM <sub>n</sub> / DIM <sub>n+1</sub>         | RS485          | Serial data for following DIM module       |

| SPARE_OUT±          | DIM <sub>n</sub> / DIM <sub>n+1</sub>         | RS485          | Reserved for internal use by AB/PO/CC      |

| SPARE_IN±           | DIM <sub>n-1</sub> / DIM <sub>n</sub>         | RS485          | Reserved for internal use by AB/PO/CC      |

| ID_IN±              | DIM <sub>n-1</sub> / DIM <sub>n</sub>         | 1-Wire<br>ID   | CERN equipment identifier                  |

| ID_OUT±             | DIM <sub>n</sub> / DIM <sub>n+1</sub>         | 1-Wire<br>ID   | CERN equipment identifier                  |

| ID_LOCAL_IN±        | User ID Local<br>Bus / DIM                    | 1-Wire<br>ID   | User equipment identifier                  |

| ID_LOCAL_OUT±       | DIM / User ID<br>Local Bus                    | 1-Wire<br>ID   | User equipment identifier                  |

Table 5-9 Connector J2 – Signal Description

Page 28 of 32

#### 5.1.3 CONNECTOR J3

This connector is reserved for programming of the DIM module CPLD integrated circuit. This will be carried out by the responsible CERN staff, during the production phase of the module, or at a later date if a firmware change is required. There shall be no interconnection to the host system with this connector.

#### 5.1.3.1 CONNECTOR TYPE

| Connector No. | Module Connector<br>Supplier/Type | Matching Connector<br>Supplier/Type |  |  |

|---------------|-----------------------------------|-------------------------------------|--|--|

| J3            | SAMTEC SSW-103-01-T-D             | -                                   |  |  |

Table 5-10 Connector J3 - Connector type

#### 5.1.3.2 PIN ALLOCATION

| J3 Pin number | Signal name |

|---------------|-------------|

| 1             | TMS         |

| 2             | TDI         |

| 3             | TDO         |

| 4             | ТСК         |

| 5             | 0V Ground   |

| 6             | +5V         |

Table 5-11 Connector J3 – Pin allocation

#### 5.1.3.3 SIGNAL DESCRIPTION

| Name      | Source/<br>Destin. | Source<br>Type<br>OC=Open<br>Collector | Function                    |

|-----------|--------------------|----------------------------------------|-----------------------------|

| TMS       | JTAG / DIM         | TTL                                    | DIM FPGA device programming |

| TDI       | JTAG / DIM         | TTL                                    | DIM FPGA device programming |

| TDO       | JTAG / DIM         | TTL                                    | DIM FPGA device programming |

| ТСК       | JTAG / DIM         | TTL                                    | DIM FPGA device programming |

| 0V Ground | DIM / JTAG         | OV                                     | DIM FPGA device programming |

| +5V       | DIM / JTAG         | +5V                                    | DIM FPGA device programming |

Table 5-12 Connector J3 – Signal Description

Page 29 of 32

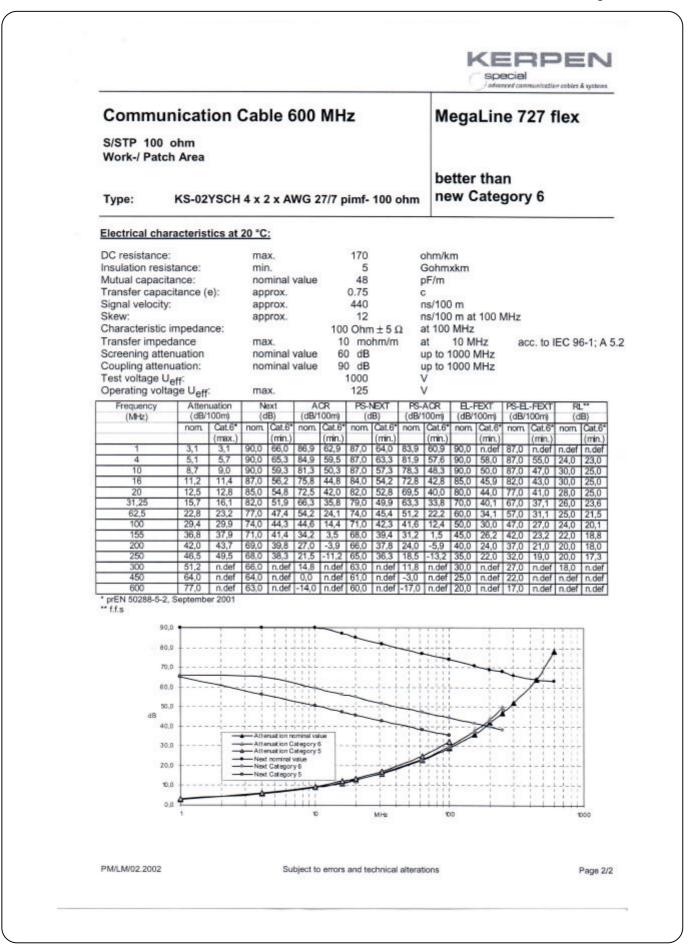

#### 5.2 MODULE INTERCONNECTING CABLE

Performance of all the Diagnostic Interface Module functions is only guaranteed where the interconnecting cable meets the following parameters:

| Name               | Value                  |  |

|--------------------|------------------------|--|

| EN 50173           | Category 5 or better   |  |

| Wire Construction  | Multi-strand           |  |

| Cable Construction | Twisted pair, Screened |  |

| Capacitance / km   | <50nF                  |  |

| Nominal Impedence  | 100 Ω                  |  |

#### Table 5-13 Interconnecting Cable Specification

The cable shall correspond to CERN safety instruction 23 for tunnel installation.

A suitable cable, available in the CERN stores, with indivdually screened pairs and an overall screen is the following:

| SCEM Nr.    | 04.21.70.104.6                 |

|-------------|--------------------------------|

| DESCRIPTION | CABLE LAN STP 4x2 AWG27/7CAT 6 |

← <u>04.21.60</u>

<u>Group: 04</u>

#### 04.21.70.B - LAN CABLE

General information : e-mail to Cern.Stores

Technical information : product manager

| CONSTRUCTION : 4 twis<br>CONDUCTOR : Cu Sn<br>INSULATION : PE cell<br>SCREENING : Polvest | AWG 27<br>Lular | /7<br>Ø 1.00 | mm    |       |     |      |

|-------------------------------------------------------------------------------------------|-----------------|--------------|-------|-------|-----|------|

| Tinned                                                                                    | conner          | braid        |       |       |     |      |

| SHEATH : Polyolefine                                                                      |                 |              |       |       |     |      |

| SPECIFICATIONS                                                                            |                 |              |       |       |     |      |

| Impedance                                                                                 | : 100           | Ohm ± 1      | 5 Ohm | (f <= | 300 | MHz) |

| Mutual capacitance                                                                        | : 48 p          | F/km         |       |       |     |      |

| Conductor resistance                                                                      | : 170           | Ohm/ km      |       |       |     |      |

| Insulation resistance                                                                     | : 5 GC          | hm/ km       |       |       |     |      |

| Propagation speed                                                                         | : 0.75          |              |       |       |     |      |

| FREQUENCY (MHz)                                                                           | 1               | 20           | 100   | 200   | 300 | 600  |

| ATTENUATION (dB/10 m)                                                                     | 0,3             | 1,3          | 2,9   | 4,2   | 5,2 | 7,8  |

#### Remarks

IS 23 SAFETY INSTRUCTION

|           | SCEM           | CONDUCT.<br>Number |     | SHEATH<br>COLOUR | TYPE        |

|-----------|----------------|--------------------|-----|------------------|-------------|

| 🕎 Buy NEW | 04.21.70.104.6 | 4 x 2              | 5,8 | grey             | CAT 6 - STP |

The manufactures data sheet is included for reference on the following pages.

#### LHC Project Document No. LHC-RFBKA-ES-000001.00 rev. 3.2

Page 30 of 32

| Mm  | Mm kg/km MJ/m            | kWh/m                                          |                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                   |

|-----|--------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.8 | 34                       | 0.35                                           | 0.1                                                                                                                                                                                 | light-grey                                                                                                                                                                                                                                                                                        | 7KS01189                                                                                                                                                                                                                                                                                                                                          |

| 5.8 | 34                       | 0.35                                           | 0.1                                                                                                                                                                                 | flame red                                                                                                                                                                                                                                                                                         | 7KS01338                                                                                                                                                                                                                                                                                                                                          |

| 5.8 | 34                       | 0.35                                           | 0.1                                                                                                                                                                                 | rape yellow                                                                                                                                                                                                                                                                                       | 7KS01034                                                                                                                                                                                                                                                                                                                                          |

| 5.8 | 34                       | 0.35                                           | 0.1                                                                                                                                                                                 | yellow green                                                                                                                                                                                                                                                                                      | 7KS01479                                                                                                                                                                                                                                                                                                                                          |

| 5.8 | 34                       | 0.35                                           | 0.1                                                                                                                                                                                 | sky blue                                                                                                                                                                                                                                                                                          | 7KS01480                                                                                                                                                                                                                                                                                                                                          |

|     | 5.8<br>5.8<br>5.8<br>5.8 | 5.8 34<br>5.8 34<br>5.8 34<br>5.8 34<br>5.8 34 | 5.8         34         0.35           5.8         34         0.35           5.8         34         0.35           5.8         34         0.35           5.8         34         0.35 | 5.8         34         0.35         0.1           5.8         34         0.35         0.1           5.8         34         0.35         0.1           5.8         34         0.35         0.1           5.8         34         0.35         0.1           5.8         34         0.35         0.1 | 5.8         34         0.35         0.1         light-grey           5.8         34         0.35         0.1         flame red           5.8         34         0.35         0.1         rape yellow           5.8         34         0.35         0.1         rape yellow           5.8         34         0.35         0.1         yellow green |

PM/LM/02.2002

Subject to errors and technical alterations

Page 1/2

Page 31 of 32

LHC Project Document No.

LHC-RFBKA-ES-000001.00 rev. 3.2

Page 32 of 32