# TMS320C672x DSP Serial Peripheral Interface (SPI)

# **Reference Guide**

Literature Number: SPRU718 October 2005

# **Contents**

| Prefa | ace     |                                                                                         | . 6       |

|-------|---------|-----------------------------------------------------------------------------------------|-----------|

| 1     | Overv   | /iew                                                                                    | . 7       |

| 2     | SPI O   | peration                                                                                | . 9       |

|       | 2.1     | Overview of SPI Operation                                                               | . 9       |

|       | 2.2     | SPI Registers                                                                           | 10        |

|       | 2.3     | SPI Operation: 3-Pin Option                                                             | 11        |

|       | 2.4     | SPI Operation: 4-Pin With Chip Select Option                                            | 13        |

|       | 2.5     | SPI Operation: 4-Pin With Enable Option                                                 | 14        |

|       | 2.6     | SPI Operation: 5-Pin Option (Enable and Chip Select)                                    | 15        |

|       | 2.7     | SPI Data Alignment in Transmit and Receive Buffers                                      | 17        |

|       | 2.8     | SPI Clocking Modes                                                                      |           |

|       | 2.9     | SPI Data Transfer Example                                                               | 21        |

|       | 2.10    | SPI Master Mode Timing Options                                                          |           |

|       | 2.11    | Robustness Features                                                                     | 23        |

| 3     | Gene    | ral Purpose I/O                                                                         | 25        |

| 4     | Low-    | Power Mode (Not Supported)                                                              | <b>26</b> |

| 5     | Emula   | ation Access and Emulation Suspend (Not Supported)                                      | <b>26</b> |

| 6     | Interr  | upts                                                                                    | 27        |

| 7     | DMA     | Interface                                                                               | 28        |

| Appe  | endix A |                                                                                         | 29        |

| A.1   | SPI R   | egisters                                                                                | 29        |

|       | A.1.1   | Introduction                                                                            | 29        |

|       | A.1.2   | SPI Global Control Register 0 (SPIGCR0)                                                 | 30        |

|       | A.1.3   | SPI Global Control Register 1 (SPIGCR1)                                                 | 31        |

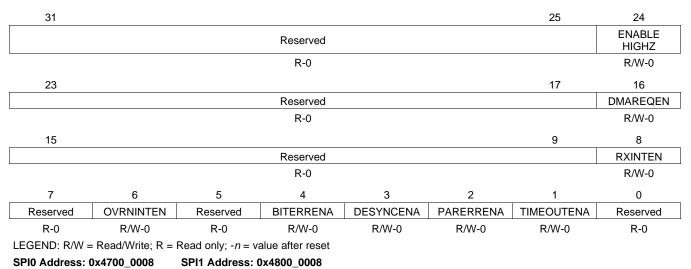

|       | A.1.4   | SPI Interrupt register (SPIINT0)                                                        | 33        |

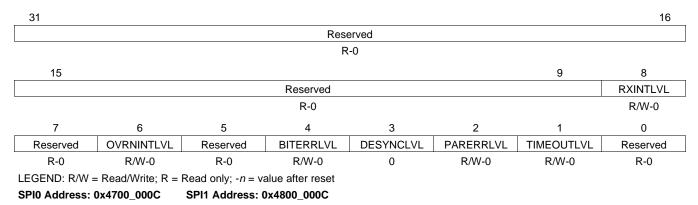

|       | A.1.5   | SPI Interrupt Level Register (SPILVL)                                                   | 35        |

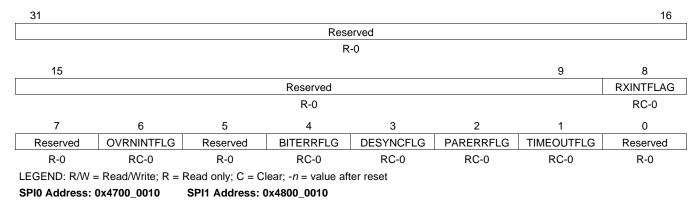

|       | A.1.6   | SPI Flag Register (SPIFLG)                                                              | 36        |

|       | A.1.7   | SPI Pin Control Register (SPIPC0)                                                       | 38        |

|       | A.1.8   | SPI Pin Control Register 1 (SPIPC1)                                                     | 39        |

|       | A.1.9   | SPI Pin Control Register 2 (SPIPC2)                                                     | 40        |

|       | A.1.10  | SPI Pin Control Register 3 (SPIPC3)                                                     | 41        |

|       | A.1.11  | <b>o</b> ( )                                                                            |           |

|       | A.1.12  | <b>ö</b> ( ,                                                                            |           |

|       | A.1.13  |                                                                                         |           |

|       | A.1.14  |                                                                                         |           |

|       | A.1.15  |                                                                                         |           |

|       | A.1.16  |                                                                                         |           |

|       | A.1.17  |                                                                                         |           |

|       | A.1.18  |                                                                                         |           |

|       | A.1.19  | 5                                                                                       |           |

|       | A.1.20  |                                                                                         |           |

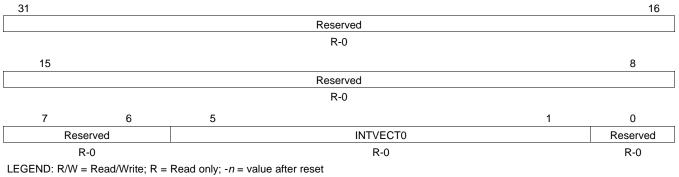

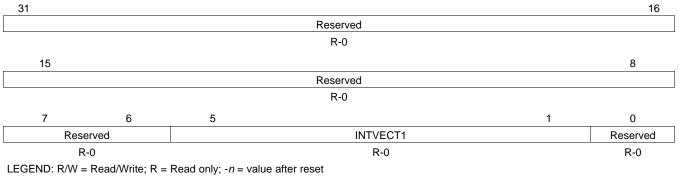

|       | A.1.21  | SPI Interrupt Vector Register 1 Transfer Group Interrupt Vector Register 1 (TGINTVECT1) | 56        |

# List of Figures

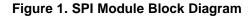

| 1    | SPI Module Block Diagram                                                                | . 7        |

|------|-----------------------------------------------------------------------------------------|------------|

| 2    | SPI 3-Pin Option                                                                        | 11         |

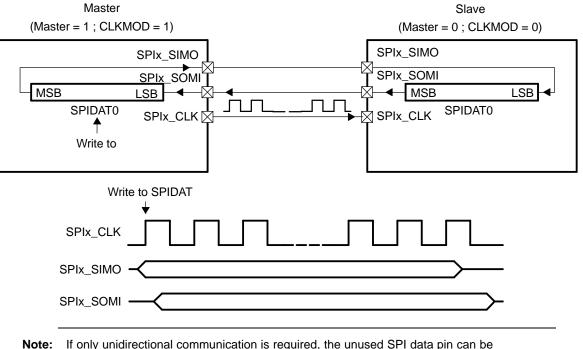

| 3    | SPI 4-Pin With Chip Select Option                                                       | 13         |

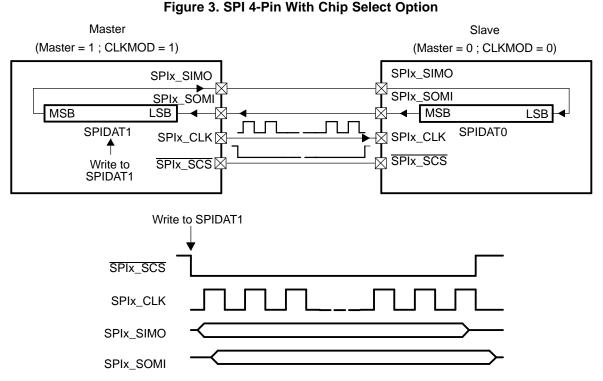

| 4    | SPI 4-Pin With Enable Option                                                            | 14         |

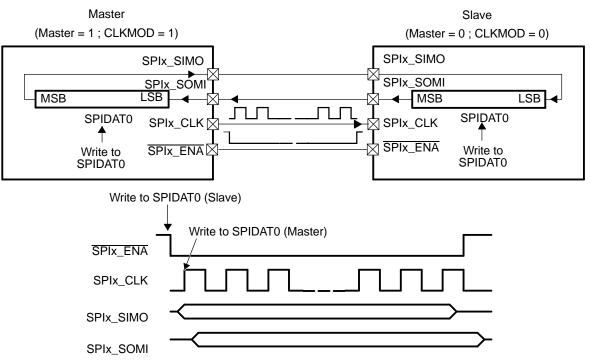

| 5    | SPI 5-Pin Option With Chip Select and Enable                                            | 15         |

| 6    | Clock Mode With POLARITY = 0 and PHASE = 0                                              | 18         |

| 7    | Clock Mode With POLARITY = 0 and PHASE = 1                                              | 19         |

| 8    | Clock Mode With POLARITY = 1 and PHASE = 0                                              | 19         |

| 9    | Clock Mode With POLARITY = 1 and PHASE = 1                                              | 20         |

| 10   | Five Bits per Character (5-Pin Option)                                                  | 21         |

| 11   | SPIFLG Interrupt Structure                                                              | 27         |

| A-1  | SPI Global Control Register 0 (SPIGCR0)                                                 | 30         |

| A-2  | SPI Global Control Register 1 (SPIGCR1)                                                 | 31         |

| A-3  | SPI Interrupt register (SPIINT0)                                                        | 33         |

| A-4  | SPI Interrupt Level Register (SPILVL)                                                   | 35         |

| A-5  | SPI Flag Register (SPIFLG)                                                              | 36         |

| A-6  | SPI Pin Control Register (SPIPC0)                                                       | 38         |

| A-7  | SPI Pin Control Register 1 (SPIPC1)                                                     | 39         |

| A-8  | SPI Pin Control Register 2 (SPIPC2)                                                     | 40         |

| A-9  | SPI Pin Control Register 3 (SPIPC3)                                                     | 41         |

| A-10 | SPI Pin Control Register 4 (SPIPC4)                                                     | 42         |

| A-11 | SPI Pin Control Register (SPIPC5)                                                       | 43         |

| A-12 | SPI Shift Register (SPIDAT0)                                                            | 44         |

| A-13 | SPI Shift register (SPIDAT1)                                                            | 45         |

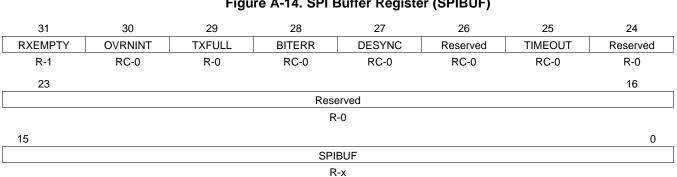

| A-14 | SPI Buffer Register (SPIBUF)                                                            | 46         |

| A-15 | SPI Emulation Register (SPIEMU)                                                         | 48         |

| A-16 | SPI Delay Register (SPIDELAY)                                                           |            |

| A-17 | Example: t <sub>C2TDELAY</sub> = 8 SYSCLK2 Cycles                                       | 49         |

| A-18 | Example: t <sub>T2CDELAY</sub> = 4 SYSCLK2 Cycles                                       | 50         |

| A-19 | Transmit Data Finished to SPIx_ENA Inactive Timeout Value                               | <b>5</b> 0 |

| A-20 | Chip Select Active to SPIx_ENA Signal Active Timeout Value                              | 51         |

| A-21 | SPI Default Chip Select Register (SPIDEF)                                               | 52         |

| A-22 | SPI Data Format Registers (SPIFMTx)                                                     | 53         |

| A-23 | SPI Interrupt Vector Register 0 Transfer Group Interrupt Vector Register 0 (TGINTVECT0) | 55         |

| A-24 | SPI Interrupt Vector Register 1 Transfer Group Interrupt Vector Register 1 (TGINTVECT1) | <b>56</b>  |

# List of Tables

| 1    | SPI Registers                                                                                              | 10 |

|------|------------------------------------------------------------------------------------------------------------|----|

| 2    | Clocking Modes                                                                                             | 18 |

| A-1  | SPI Registers                                                                                              | 29 |

| A-2  | SPI Global Control Register 0 (SPIGCR0) Field Descriptions                                                 | 30 |

| A-3  | SPI Global Control Register 1 (SPIGCR1) Field Descriptions                                                 | 31 |

| A-4  | SPI Interrupt register (SPIINT0) Field Descriptions                                                        | 33 |

| A-5  | SPI Interrupt Level Register (SPILVL) Field Descriptions                                                   | 35 |

| A-6  | SPI Flag Register (SPIFLG) Field Descriptions                                                              | 36 |

| A-7  | SPI Pin Control Register (SPIPC0) Field Descriptions                                                       | 38 |

| A-8  | SPI Pin Control Register 1 (SPIPC1) Field Descriptions                                                     | 39 |

| A-9  | SPI Pin Control Register 2 (SPIPC2) Field Descriptions                                                     | 40 |

| A-10 | SPI Pin Control Register 3 (SPIPC3) Field Descriptions                                                     | 41 |

| A-11 | SPI Pin Control Register 4 (SPIPC4) Field Descriptions                                                     | 42 |

| A-12 | SPI Pin Control Register (SPIPC5) Field Descriptions                                                       | 43 |

| A-13 | SPI Shift Register (SPIDAT0) Field Descriptions                                                            | 44 |

| A-14 | SPI Shift register (SPIDAT1) Field Descriptions                                                            | 45 |

| A-15 | SPI Buffer Register (SPIBUF) Field Descriptions                                                            | 46 |

| A-16 | SPI Emulation Register (SPIEMU) Field Descriptions                                                         | 48 |

| A-17 | SPI Delay Register (SPIDELAY) Field Descriptions                                                           | 49 |

| A-18 | SPI Default Chip Select Register (SPIDEF) Field Descriptions                                               | 52 |

| A-19 | SPI Data Format Registers (SPIFMTx) Field Descriptions                                                     | 53 |

| A-20 | SPI Interrupt Vector Register 0 Transfer Group Interrupt Vector Register 0 (TGINTVECT0) Field Descriptions | 55 |

| A-21 | SPI Interrupt Vector Register 1 Transfer Group Interrupt Vector Register 1 (TGINTVECT1) Field Descriptions |    |

Preface SPRU718–October 2005

#### About This Manual

This reference guide provides the specifications for a 16-bit configurable, synchronous serial peripheral interface. The SPI is a programmable-length shift register, used for high speed communication between external peripherals or other microcontrollers

#### **Notational Conventions**

The TMS320C672x<sup>™</sup> DSP has two SPI modules. This document describes both modules. Where pins are described, the pin name is listed as SPIx\_<suffix>. The 'x' is either '0' for SPI0 or '1' for SPI1.

When describing particular bits, the convention REGISTER.BIT(s) is used. For example, bit 0 of the SPIGCR0 register (the RESET bit) is referred to as SPIGCR0.RESET.

#### **Related Documentation From Texas Instruments**

The following documents describe the C6000<sup>™</sup> devices and related support tools. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

TMS320C672x DSP Peripherals Overview Reference Guide (literature number <u>SPRU723</u>) describes peripherals available on the TMS320C672x<sup>™</sup> DSPs.

*TMS320C6713 to TMS320C672x Migration Guide* (literature number <u>SPRAA78</u>) describes the issues related to migrating from the TMS320C6713 to the TMS320C672x<sup>™</sup> floating-point digital signal processors.

TMS320C672xDSP CPU and Instruction Set Reference Guide (literature number <u>SPRU733</u>) describes the TMS320C672x<sup>™</sup> CPU architecture, instruction set, pipeline, and interrupts for these digital signal processors.

#### **Trademarks**

All other trademarks are the property of their respective owners.

# TMS320C672x DSP Serial Peripheral Interface (SPI)

#### 1 Overview

This reference guide describes the TMS320C672x Serial Peripheral Interface Module (SPI). The SPI is a synchronous, full-duplex serial port which supports 3-, 4-, and 5-pin options. Figure 1 contains a block diagram of the SPI module. The major SPI components are:

- 16-bit shift register (SPIDAT0)

- Combined 16-bit shift register and format selection register (SPIDAT1)

- 16-bit receive buffer register (SPIBUF)

- 16-bit receive buffer emulation 'alias' register (SPIEMU)

- 8-bit baud clock generator

- Serial clock (SPIx\_CLK) I/O pin

- Slave in, master out (SPIx\_SIMO) I/O pin

- Slave out, master in (SPIx\_SOMI) I/O pin

- SPI enable (SPIx\_ENA) I/O pin (4- or 5-pin mode only)

- Slave chip select (SPIx\_SCS) I/O pin (4- or 5-pin mode only)

- Programmable clock divider, including polarity and phase options.

- Interrupt capability

Overview

The SPI allows software to program the following options:

- Master or Slave Mode

- SPIx\_CLK frequency (interface clock [SYSCLK2] /8 through /256)

- SPI pins as functional or digital I/O pins

- Character length (2 to 16 bits)

- Phase (delay/no delay), Polarity (high or low)

- Programmable delay between transmissions in master mode

- Chip select to clock delay insertion in master mode

- Chip select hold mode for master

## 2 SPI Operation

This section describes the operation modes of the SPI. First it gives and overview of SPI operation and then provides details on the 3-, 4-, and 5-pin options, as well as more specific details on the supported data formats.

#### 2.1 Overview of SPI Operation

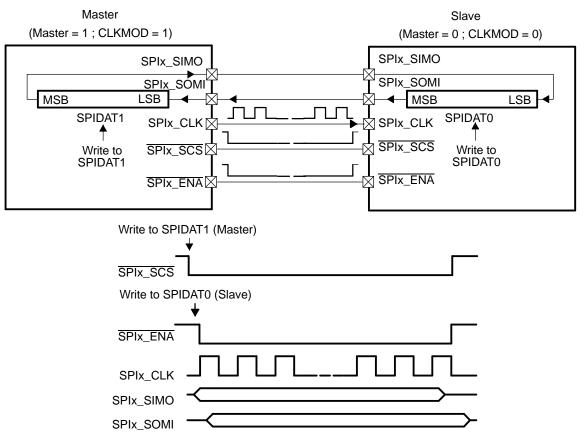

The SPI operates in master or slave mode. The SPI bus master is the device which drives the SPIx\_CLK, SPIx\_SIMO, and optionally the SPIx\_SCS signals, and therefore initiates SPI bus transfers. SPIGCR1.CLKMOD and SPIGCR1.MASTER select between master and slave mode.

In both master and slave mode, the SPI supports four options:

- 3-pin option: See Section 2.3.

- 4-pin with chip select option: See Section 2.4.

- 4-pin with enable option: See Section 2.5.

- 5-pin option (with enable and chip select): See Section 2.6.

The 3-pin option is the basic clock, data in, and data out SPI interface and uses the SPIx\_CLK, SPIx\_SIMO, and SPIx\_SOMI pins. The 4-pin with chip select option adds the SPIx\_SCS pin which is used to support multiple SPI slave devices on a single SPI bus. The 4-pin with enable option adds the SPIx\_ENA pin which is used to increase the overall throughput by adding hardware handshaking. The 5-pin option uses all the SPI pins and is a superset of the different options.

#### 2.2 SPI Registers

A list of the C672x device SPI0 and SPI1 module internal registers is contained in Table 1.

|              |              | •          |                                 |                                                                                       |

|--------------|--------------|------------|---------------------------------|---------------------------------------------------------------------------------------|

| SPI0 Address | SPI1 Address | Mnemonic   | Name                            | Description                                                                           |

| 0x4700 0000  | 0x4800 0000  | SPIGCR0    | Global Control Register 0       | Contains the Software Reset bit for the module                                        |

| 0x4700 0004  | 0x4800 0004  | SPIGCR1    | Global Control Register 1       | Controls basic configurations of the module                                           |

| 0x4700 0008  | 0x4800 0008  | SPIINT0    | Interrupt Register              | Enables bits for interrupts, error, DMA and other functionality                       |

| 0x4700 000C  | 0x4800 000C  | SPILVL     | Interrupt Level Register        | SPI Interrupt Levels are set in this register                                         |

| 0x4700 0010  | 0x4800 0010  | SPIFLG     | Interrupt Flag Register         | Shows the status of several events during the operation                               |

| 0x4700 0014  | 0x4800 0014  | SPIPC0     | Pin Control Register 0          | Determines if pins will operate as general I/O or SPI functional pin                  |

| 0x4700 0018  | 0x4800 0018  | SPIPC1     | Pin Control Register 1          | Controls the direction of data on the I/O pins                                        |

| 0x4700 001C  | 0x4800 001C  | SPIPC2     | Pin Control Register 2          | Reflects the values on the I/O pins                                                   |

| 0x4700 0020  | 0x4800 0020  | SPIPC3     | Pin Control Register 3          | Controls the values sent to the I/O pins                                              |

| 0x4700 0024  | 0x4800 0024  | SPIPC4     | Pin Control Register 4          | Sets data values in the SPIPC3 register                                               |

| 0x4700 0028  | 0x4800 0028  | SPIPC5     | Pin Control Register 5          | Clears values in the SPIPC3 register                                                  |

| 0x4700 002C  | 0x4800 002C  | Reserved   | Reserved                        | Reserved - Do not write to this register                                              |

| 0x4700 0030  | 0x4800 0030  | Reserved   | Reserved                        | Reserved - Do not write to this register                                              |

| 0x4700 0034  | 0x4800 0034  | Reserved   | Reserved                        | Reserved - Do not write to this register                                              |

| 0x4700 0038  | 0x4800 0038  | SPIDAT0    | Shift Register 0                | Main shift register                                                                   |

| 0x4700 003C  | 0x4800 003C  | SPIDAT1    | Shift Register 1                | Shift register used in automatic slave chip<br>select mode only                       |

| 0x4700 0040  | 0x4800 0040  | SPIBUF     | Buffer Register                 | Holds received word                                                                   |

| 0x4700 0044  | 0x4800 0044  | SPIEMU     | Emulation Register              | Mirror of SPIBUF. Read does not clear flags                                           |

| 0x4700 0048  | 0x4800 0048  | SPIDELAY   | Delay Register                  | Sets SPIx_SCS mode, SPIx_SCS<br>pre-/post-transfer delay time and SPIx_ENA<br>timeout |

| 0x4700 004C  | 0x4800 004C  | SPIDEF     | Default Chip Select<br>Register | In SPIx_SCS decoded mode only: sets high<br>low/active SPIx_SCS signals               |

| 0x4700 0050  | 0x4800 0050  | SPIFMT0    | Format 0 Register               | Configuration of data word format 0                                                   |

| 0x4700 0054  | 0x4800 0054  | SPIFMT1    | Format 1 Register               | Configuration of data word format 1                                                   |

| 0x4700 0058  | 0x4800 0058  | SPIFMT2    | Format 2 Register               | Configuration of data word format 2                                                   |

| 0x4700 005C  | 0x4800 005C  | SPIFMT3    | Format 3 Register               | Configuration of data word format 3                                                   |

| 0x4700 0060  | 0x4800 0060  | TGINTVECT0 | TG Interrupt Vector             | Transfer group interrupt vector for line SPI INT0                                     |

| 0x4700 0064  | 0x4800 0064  | TGINTVECT1 | TG Interrupt Vector             | Transfer group interrupt vector for line SPI INT1                                     |

# Table 1. SPI Registers

# 2.3 SPI Operation: 3-Pin Option

The 3-pin option for SPI operation uses only the clock (SPIx\_CLK), and data (SPIx\_SOMI and SPIx\_SIMO) pins for bidirectional communication between master and slave devices. Figure 2 illustrates the basic 3-pin SPI option.

To select the 3-pin SPI option, the SPIx\_CLK, SPIx\_SOMI, and SPIx\_SIMO pins should be configured as functional pins and the SPIx\_SCS and SPIx\_ENA pins should be configured as general purpose I/O pins by writing 0x0E00 to SPIPC0.

#### Figure 2. SPI 3-Pin Option

**Note:** If only unidirectional communication is required, the unused SPI data pin can be configured as GPIO. This is true for all SPI modes (not just 3-pin).

The SPI can operate in either master or slave mode. The SPI bus master is the device which drives the SPIx\_CLK signal and therefore initiates SPI bus transfers. The SPIGCR1.CLKMOD and SPIGCR1.MASTER bits select between master and slave mode; both must be programmed to '1' to configure the SPI for master mode or '0' to configure the SPI for slave mode.

In master mode with the 3-pin option, the DSP writes transmit data to the SPIDAT0 or the SPIDAT1 register. This initiates a transfer. A series of clocks pulses will be driven out on the SPIx\_CLK pin to complete the transfer. Each clock pulse on the SPIx\_CLK pin causes the simultaneous transfer (in both directions) of one bit by both the master and slave SPI devices.

Whether in master or slave mode, the word length must be configured in the SPIFMTx.CHARLEN[4:0] field before the first transfer is initiated. The word length must match the number of clock pulses per transfer expected on the SPIx\_CLK pin. Note that there are four different format registers: SPIFMT0, SPIFMT1, SPIFMT2, and SPIFMT3. The format register that applies is selected by SPIDAT1.DFSEL[1:0]. The default format register is SPIFMT0 since SPIDAT1.DFSEL[1:0] defaults to '00'.

In addition to the word length, the SPIFMTx register selects the clock polarity and phase, the shift direction, and if enabled, the delay, to insert automatically between transactions. Examples of clock polarity and phase options are given in Section 2.8.

Data should be written to the shift register (either SPIDAT0[15:0] or SPIDAT1[15:0]) right aligned. (If there is receive data from a previous transfer, this should be read out of the SPIBUF register first, since the write to the shift register will cause the next transfer to begin). In addition, if the SPI is operating in slave mode, then the write to the shift register must occur before the first clock pulse from the master occurs.

The SPI automatically selects the appropriate bits from the right aligned data in the shift register and shifts these out on the transmit data pin. At the same time, data is shifted in from the receive pin. In master mode the transmit data pin is SPIx\_SIMO and the receive data pin is SPIx\_SOMI. In slave mode the roles are reversed, SPIx\_SIMO is the receive data pin and SPIx\_SOMI is the transmit data pin.

When all of the bits have been transferred, the received data is copied to the SPIBUF register for the DSP or dMAX to read. Data is stored right-justified in SPIBUF and realigned automatically if needed by the SPI module.

In addition, the following actions occur:

- The interrupt flag SPIFLG.RXINTFLAG bit is set to 1

- An interrupt is asserted if the SPIINT0.RXINTEN bit is set to 1

# 2.4 SPI Operation: 4-Pin With Chip Select Option

The 4-pin with chip select option is a superset of the 3-pin option. Figure 3 illustrates the SPI used with this option.

An additional pin, <u>SPIx\_SCS</u>, is used in this mode. The <u>SPIx\_SCS</u> pin must be configured to be functional (SPIPC0.SCSFUN0 = 1) in addition to the SPIx\_CLK, SPIx\_SIMO, and SPIx\_SOMI pins. To select this mode, write 0x0E01 to SPIPC0.

In slave mode with the chip select option enabled, the SPI ignores all transactions on the bus unless SPIx\_SCS is asserted by the bus master. It also 3-states its output pin when SPIx\_SCS is deasserted by the master to avoid conflicting with the active slave device on the bus.

In master mode, the SPIx\_SCS pin functions as an output, and toggles when a specific slave device is selected. However, this is most useful on devices which support multiple SPIx\_SCS pins. The C672x DSP only supports a single SPIx\_SCS and so the usefulness of this pin in master mode is limited. In practice, general purpose I/O pins will be needed to support multiple slave device chip selects.

However, one reason to use the SPIx\_SCS pin as a functional pin for the SPI master is to take advantage of the timing parameters which can be set using the SPIDELAY register. This register allows delays to be added automatically so that the slave timing requirements between clock and chip select may be more easily met. See Section A.1.17 for additional details. Another reason would be to make use of the error detection built into the SPI (seeSection 2.11).

#### CAUTION

Avoid prematurely deasserting the SPIx\_SCS signal. The slave SPI does not support 'aborting' a transfer by removing the SPIx\_SCS before the selected number of SPIx\_CLK pulses have been received. If this does occur, the slave SPI will most likely lose synchronization with the master SPI and this could corrupt subsequent transfers. This happens because although the slave SPI will 3-state the data output pin within a few SYSCLK2 cycles of SPIx\_SCS deasserted, the SPI internal state machines still expect to see the master drive the remaining SPIx\_CLK cycles as determined by the SPIFMTx.CHARLEN[4:0] value.

# 2.5 SPI Operation: 4-Pin With Enable Option

The 4-pin with enable option is also a superset of the 3-pin option. Figure 4 illustrates the SPI used with this option.

Figure 4. SPI 4-Pin With Enable Option

To use the SPIx\_ENA as a handshake signal pin, the SPIx\_ENA pin must be configured to be functional (SPIPC0.ENABLEFUN = 1) in addition to the SPIx\_CLK, SPIx\_SIMO, and SPIx\_SOMI pins. To select this mode, write 0x0F00 to SPIPC0.

The handshake operation works this way:

- After a transfer completes, both the master and slave SPI modules need to be serviced.

- The slave SPI deasserts SPIx\_ENA after the transfer, indicating it requires servicing and is not ready.

- The slave should begin servicing its SPI by reading receive data from SPIBUF first.

- Next, the slave device should write transmit data to SPIDAT0 or SPIDAT1. This causes the slave SPI to assert SPIx\_ENA indicating it is ready for the next transmission.

- In parallel, the master device can service its SPI at any time. It does not need to insert a delay before

writing to its SPIDAT0 or SPIDAT1 registers in order to avoid overrunning the slave device. Instead,

the master SPI module will automatically delay the next transfer until the slave has asserted SPIx\_ENA

again to indicate it is ready for the transmission.

This handshake allows the two SPIs to communicate at the maximum rate possible. Without the handshake pin, the master must insert a delay between each transfer long enough to support the worst case response time of the slave servicing its SPI or risk an overrun condition. With the handshake, the throughput is determined by the average response time of the two devices servicing their SPI ports.

The SPIx\_ENA pin can be driven in a push-pull or open drain mode, depending upon the setting of the SPIINT0.ENABLE HIGHZ bit.

# 2.6 SPI Operation: 5-Pin Option (Enable and Chip Select)

The 5-pin mode is a superset of both 4-pin modes. To use the 5-pin mode, both the SPIx\_ENA pin and SPIx\_SCS pin must be configured as functional pins (SPIPC0.SCSFUN0 = 1 and SPIPC0.ENABLEFUN = 1), in addition to the SPIx\_CLK, SPIx\_SIMO, and SPIx\_SOMI pins. To select this mode, write 0x0F01 to SPIPC0. Figure 5 illustrates the SPI used with the 5-pin option.

#### Figure 5. SPI 5-Pin Option With Chip Select and Enable

For the 5-pin option, in general the behavior of the enable and chip select features are the same as described in Section 2.4 and Section 2.5.

However, there is some additional interaction between the SPIx\_SCS and SPIx\_ENA pins in the 5-pin mode:

- 1. The assertion of SPIx\_ENA by the slave is delayed until the master asserts SPIx\_SCS.

- 2. The SPIINT0.ENABLE HIGHZ must be set to '1' in 5-pin mode, and an external pullup resistor of appropriate strenght is required.

- 3. Chip select hold (SPIDAT1.CSHOLD) cannot be used in 5-pin mode.

The first interaction above is intended to allow the use of the enable option even when there are multiple SPI slaves on a single SPI bus, each slave with its own enable pin.

The second interaction is due to timing constraints. On C672x devices, the master must see the SPIx\_ENA pin deasserted practically immediately after it asserts SPIx\_ENA. The only way to meet this timing requirement is to have SPIx\_ENA deasserted before the SPIx\_SCS pin is asserted. To meet this requirement, the SPIx\_ENA pin must be pulled up with a resistor strong enough to ensure the SPIx\_ENA pin returns to a logic '1' in the time the SPIx\_SCS pin is deasserted (including any time it takes the previously selected slave device to 3-state its SPIx\_ENA after it recognizes SPIx\_SCS as deasserted.

SPI Operation

The third interaction is also due to timing constraints. If SPIDAT1.CSHOLD is enabled (and therefore <u>SPIx\_SCS</u> remains asserted between transfers) on the master, then the slave must deassert the <u>SPIx\_ENA</u> pin almost immediately after the final edge of the SPIx\_CLK pin. The C672x SPI slave does not meet this requirement; therefore, the combination of the SPIDAT1.CSHOLD feature and the 5-pin mode should not be used, enabled together.

#### CAUTION

Avoid prematurely deasserting the SPIx\_SCS signal. The slave SPI does not support 'aborting' a transfer by removing the SPIx\_SCS before the selected number of SPIx\_CLK pulses have been received. If this does occur, the slave SPI will most likely lose synchronization with the master SPI and this could corrupt subsequent transfers. This happens because although the slave SPI will 3-state the data output pin within a few SYSCLK2 cycles of SPIx\_SCS deasserted, the SPI internal state machines still expect to see the master drive the remaining SPIx\_CLK cycles as determined by the SPIFMTx.CHARLEN[4:0] value.

#### CAUTION

Additionally, in 5-pin mode the slave device will continue to drive the SPIx\_ENA pin if the SPIx\_SCS is deasserted prematurely.

# 2.7 SPI Data Alignment in Transmit and Receive Buffers

The SPI module supports several data formatting options:

- Shift direction: MSB or LSB first (SPIFMTx.SHIFTDIR)

- Character Length: 2 to 16 bits (SPIFMTx.CHARLEN

For example, you might configure the SPI to transmit MSB first, with a character length of 7 bits, and wish to transmit the binary sequence '100 0000b'. Since the shift register size is 16 bits and the MSB first option is selected, it is natural to think that you might need to shift the binary sequence to the MSB position using the CPU, before writing data to the SPI module. For example, writing "1000 0000 0000 0000b" to SPIDAT0 or SPIDAT1. However, the C672x SPI module automatically performs this shift based upon the settings in SPIFMTx.SHIFTDIR and SPIFMTx.CHARLEN. Therefore, the SPIDAT0 or SPIDAT1 register should be written with "0000 0000 0100 0000" (no shift required).

The SPI also realigns incoming receive data automatically. For example, if the SPI is configured for LSB first bit order (so that receive data is shifted into MSB of the shift register) then if the same seven bits are shifted into the SPI in the order of "100 0000b" where the first bit to shift in is the '1b', then the shift register would normally contain "0000 001x xxxx xxxxb" after the transfer, where 'x' means bits that are not part of the current transfer.

However, before copying this data to the SPIBUF register, the SPI automatically realigns the data so that it is right-justified. In addition, it replaces the 'x' bits with '0'. So in the receive example, the SPIBUF register will read "0000 0000 0000 0001b."

To summarize: data is always written to SPIDAT0/SPIDAT1 and read from SPIBUF by the DSP or dMAX right aligned. The term right aligned means that the LSB of the data word is always aligned to bit zero of the buffer register. This is true regardless of character length or shift direction. The SPI automatically corrects for the character length and shift direction settings.

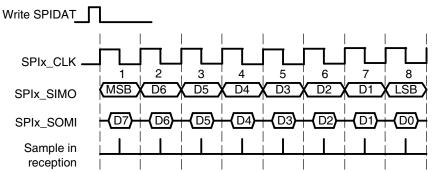

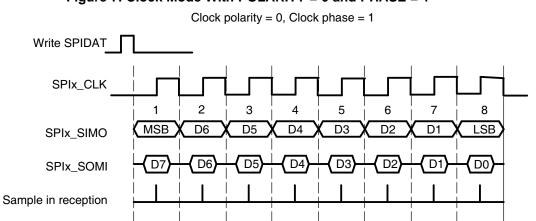

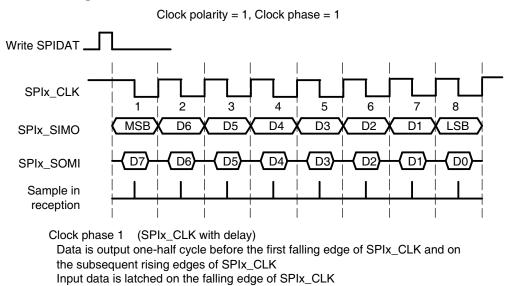

#### 2.8 SPI Clocking Modes

There are four clock modes in which SPIx\_CLK may operate, depending on the choice of the phase (delay/no delay) and the polarity (rising edge/falling edge) of the clock. When operating with PHASE active, the SPI makes the first bit of data available after the SPIDAT0 register is written and before the first edge of SPIx\_CLK. The data input and output edges depend on the values of both POLARITY and PHASE as shown in Table 2.

| Polarity | Phase | Action                                                                                                                                                         |

|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | 0     | Data is output on the rising edge of SPIx_CLK. Input data is latched on the falling edge.                                                                      |

| 0        | 1     | Data is output one half-cycle before the first rising edge of SPIx_CLK and on subsequent falling edges. Input data is latched on the rising edge of SPIx_CLK.  |

| 1        | 0     | Data is output on the falling edge of SPIx_CLK. Input data is latched on the rising edge.                                                                      |

| 1        | 1     | Data is output one half-cycle before the first falling edge of SPIx_CLK and on subsequent rising edges. Input data is latched on the falling edge of SPIx_CLK. |

#### Table 2. Clocking Modes

Figure 6 through Figure 9 illustrate the four possible signals of SPIx\_CLK corresponding to each mode. Having four signal options allows the SPI to interface with different types of serial devices. Also shown are the SPIx\_CLK control bit polarity and phase values corresponding to each signal.

#### Figure 6. Clock Mode With POLARITY = 0 and PHASE = 0

Clock polarity = 0, Clock phase = 0

Clock phase = 0 (SPIx\_CLK without delay) Data is output on the rising edge of SPIx\_CLK Input data is latched on the falling edge of SPIx\_CLK A write to the SPIDAT register starts SPIx\_CLK

Figure 7. Clock Mode With POLARITY = 0 and PHASE = 1

Clock phase = 1 (SPIx\_CLK with delay)

Data is output one-half cycle before the rising of SPIx\_CLK

and on subsequent falling edges of SPIx\_CLK input data is latched on the rising edge of SPIx\_CLK

Figure 8. Clock Mode With POLARITY = 1 and PHASE = 0

Clock phase = 0 (SPIx\_CLK without delay) Data is output on the falling edge of SPIx\_CLK Input data is latched on the rising edge of SPIx\_CLK A write to the SPIDAT register starts SPIx\_CLK

#### Figure 9. Clock Mode WIth POLARITY = 1 and PHASE = 1

# 2.9 SPI Data Transfer Example

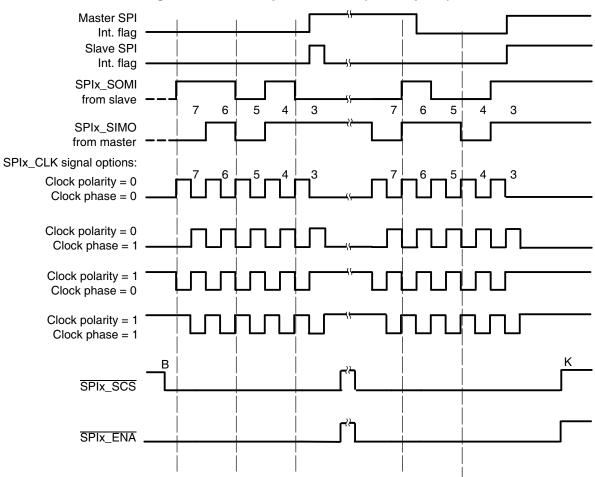

Figure 10 illustrates an SPI data transfer between two devices using a character length of five bits.

#### Figure 10. Five Bits per Character (5-Pin Option)

#### 2.10 SPI Master Mode Timing Options

The SPI in master mode supports several options to modify the timing of its generation of the chip select signal (SPIx\_SCS). This allows the SPI to support the timing requirements of various slave devices without adding additional overhead to the DSP by generating the appropriate delays automatically.

#### 2.10.1 Chip Select Setup Time

The master can be configured to provide a (slow) slave device a certain chip select setup time to the first edge on SPIx\_CLK. This delay is controlled by the SPIDELAY.C2TDELAY bit field and can be configured between for 2 and 33 SYSCLK2 cycles.See Section A.1.17

#### 2.10.2 Chip Select Hold Time

The master can also be configured to provide a (slow) slave device a certain chip select hold time after the last edge on SPIx\_CLK. This delay is controlled by the SPIDELAY.T2CDELAY bit field and can be configured between for 1 and 32 SYSCLK2 cycles.See Section A.1.17

#### 2.10.3 Automatic Delay Between Transfers

The SPI master can automatically insert a delay of between 2 and 65 SYSCLK2 cycles following a transmission. The next transmission will not begin until the delay has ended. The delay count is configured in the SPIFMTx.WDELAY bit field. The delay must also be enabled by setting SPIDAT1.WDEL.

#### 2.10.4 SPI Chip Select Hold Option

There are slave devices available that require the chip select signal to be held continuously active during several consecutive data word transfers. Other slave devices require the chip select signal to be deactivated between consecutive data word transfers.

The SPI can support both types of slave devices. The SPIDAT1.CSHOLD bit selects between the two options.

If the chip select hold option is enabled, the chip select will not toggle between two consequitive accesses. Therefore the SPIDELAY.T2CDELAY of the first transfer and the SPIC2TDELAY of the second transfer will not be applied.

However, the wait delay could be still applied between the two transactions, if the bit SPIDAT1.WDEL is set.

**Note:** If the SPIDAT1.CSHOLD bit is set within the control field, the current hold time and the following setup time will not be applied in between transaction.

**Note:** If the SPIDAT1.CSHOLD bit is set within the control field, the current hold time and the following setup time will not be applied in between transaction.

# 2.11 Robustness Features

The C672x SPI includes many features to make the SPI communication link robust. A loopback test mode can be used to facilitate a power on self test routine. Additionally, the SPI master continually monitors the bus for faults on its data line. The handshaking between master and slave can be monitored as well, and appropriate actions can be taken (interrupt, timeout) when the handshake breaks down. The following sections describe these robustness features in more detail.

## 2.11.1 SPI Internal Loop-Back Test Mode (Master Only)

The internal loop-back self-test mode can be utilized to test the SPI transmit path and receive path including the transmit and receive buffers. In this mode the transmit signal is internally fed back to the receiver and the SPIx\_SIMO, SPIx\_SOMI and SPIx\_CLK pins remain static.

This mode allows the DSP to write into the transmit buffer, and check that the receive buffer contains the correct transmit data. If an error occurs the corresponding error is set within the status field.

CAUTION This mode cannot be changed during a transmission.

#### 2.11.2 SPI Transmission Continuous Self-test (Master Only)

During a data transfer, the SPI master inputs the value from its data output pin on the appropriate SPIx\_CLK edge. This value is compared against the expected value and any difference indicates a fault on the SPI bus. If a fault is detected, then the SPIBUF.BITERR and SPIFLG.BITERRFLG bits are set and an error interrupt is generated if enabled.

#### 2.11.3 SPI Detection of Slave Desynchronization

In the 4-pin with enable and 5-pin modes, the SPI master can monitor the slave SPIx\_ENA activity to detect a desynchronization event.

Some conditions which may cause a desynchronization event are:

- · Master or slave device being reset during a transmission

- Asserting a software reset of the SPI module during transmission

- Having an incorrect SPI pin configuration, causing the SPIx\_ENA pin to behave incorrectly

- Signal integrity problem causing additional clocks to be recognized by the slave

The master can detect two desynchronization error conditions on the SPIx\_ENA pin:

- 1. Slave deasserts SPIx\_ENA after a tranmission has begun, but before it completes.

- 2. Slave fails to deassert SPIx\_ENA within a certain time period after the completion of the last bit of the tranmission.

The first error condition is straighforward to detect. To detect the second error condition, the SPI module includes an eight bit counter with a timeout count that can be configured through the SPIDELAY.T2EDELAY bit field.

When a desynchronization event is detected, the master SPIBUF.DESYNC and SPIFLG.DESYNCFLG flags are set and a desynchronization error interrupt is asserted if enabled.

**Note:** Remember that even though the desynchronization is detected by the master device, the problem causing the desynchronization event can be on either the master or the slave device.

## 2.11.4 SPIx\_ENA Signal Timeout

In 5-pin mode, in addition to the desynchronizations event described in Section 2.11.3, the master can also detect whether the slave fails to respond to the SPIx\_SCS signal by asserting SPIx\_ENA in a timely manner.

This condition could be the result of a serious error, or it could simply be the result of the slave device taking too long to service its SPI.

To detect this condition, the SPI includes an 8-bit timeout counter. The counter time out value is configurable through the SPIDELAY.C2EDELAY bit field. If the timeout counter expires before an active SPIx\_ENA signal is sampled the SPIFLG.TIMEOUTFLG and SPIBUF.TIMEOUT flags are set. An interrupt will be generated if enabled.

#### 3 General Purpose I/O

Each of the SPI pins may be programmed via the SPI Pin Control Registers (SPIPC0, SPIPC1, SPIPC2, SPIPC3, SPIPC4, SPIPC5) to be a general-purpose I/O pin.

Whenever one of the the SPI module pins is not used for chosen SPI bus protocol, the unused pins should be programmed to be either general-input or general-output pins by setting the corresponding bit in SPIPC0 to '0'.

For example, in 3-pin mode, SPIx\_SOMI, SPIx\_SIMO, and SPIx\_CLK must be configured as SPI pins, while the SPIx\_SCS and SPIx\_ENA pins should be configured as GPIO.

The direction of the pin is controlled in the SPIPC1 register. If configured as a general purpose output, then the SPIPC3 register controls the output value.

There is also a write '1' to set (SPIPC4) and write '1' to clear (SPIPC5) register for the data out value. These registers allow different tasks running on the DSP to manipulate the SPI I/O pins without read-modify-write hazards.

The SPIPC2 register always reflects the value input from the pin.

Low-Power Mode (Not Supported)

#### 4 Low-Power Mode (Not Supported)

The SPI module does not support low power mode on C672x DSPs.

Do not program the SPIGCR1.POWERDOWN bit to '1'. The behavior of the SPI is undefined if this bit is set.

#### 5 Emulation Access and Emulation Suspend (Not Supported)

The C672x DSP does not support emulation accesses or emulation suspend for its peripherals. This means that the SPI will continue to operate while the DSP has been halted through the use of a JTAG emulator.

In addition, any status registers that are cleared after reading will be affected if viewed in a memory or watch window of the debugger; since the emulator will read these registers to update the value displayed in the window.

CAUTION Viewing or otherwise reading the following SPI registers: SPIBUF, SPIFLG, TGINTVECT0, TGINTVECT1 through the JTAG debugger will cause their contents to change, possibly invalidating the results of the debug session. Be sure to set up the debugger to avoid reading these registers. The SPI module generates interrupts and provides separate interrupt vectors on two levels; however these are combined into a single interrupt request along with interrupts from the I2C modules and the other SPI module to create INT14 on the C672x DSP.

It is STRONGLY RECOMMENDED to use CPU INT14 only for SPI error interrupts, and to use the SPI module DMA interface to generate data transfer requests. Interrupts are enabled using the SPIINT0 register (Section A.1.4).

Also, since the two interrupt levels of the SPI are combined to generate a single interrupt request to the CPU, it is also recommended to make use of only interrupt level 0 and leave interrupt level 1 unused. Interrupt level assignments are configurable in the SPILVL register (Section A.1.5).

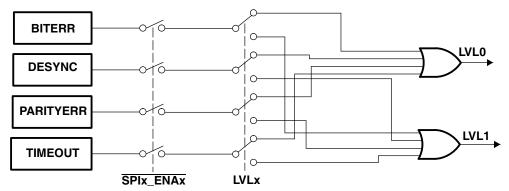

When an interrupt condition occurs, the bit indicating this condition is set in the SPIFLG register (Section A.1.6). If this condition is configured to generate an interrupt (if the SPIINTO register enable bit for this condition is set) then the interrupt is routed to one of the two levels. The level for each interrupt is controlled by the SPILVL register.

For each level, the SPI combines with a logical 'OR' all of the SPIFLG bits that are both enabled and configured for this level. This is illustrated in Figure 11.

Then at the chip level, two interrupt requests from SPI0, the two interrupt requests from SPI1, the I2C0, and the I2C1 interrupt request lines are combined with a logical 'OR' to generate CPU INT14.

#### Figure 11. SPIFLG Interrupt Structure

#### CAUTION

The CPU interrupt request line INT14 is rising edge sensitive. This means that if any one of the interrupt flags enabled to generate INT14 remains set, the INT14 line will remain at a logic '1' and all other interrupts will be blocked. Therefore any interrupt enabled for CPU INT14 must be cleared promptly or it will block other interrupts on the same line.

#### CAUTION

In addition, before exiting the INT14 ISR, the DSP must make sure that the (enabled) interrupt flags in all peripherals assigned to use INT14 have been cleared. Otherwise, further interrupts may be blocked by the peripheral with the unserviced interrupt request.

#### CAUTION

In addition to the above caution, it should be noted that after a CPU INT14 is generated, all of the modules which have been configured to generate INT14 should be checked for interrupt status. It is quite possible that more than one module has generated an interrupt request simultaneously, but that only one CPU interrupt results.

DMA Interface

#### 7 DMA Interface

The SPI supports a DMA interface for transmit and receive data transfers.

It is STRONGLY RECOMMENDED to use the SPI DMA interface for data transfers, and limit the use of interrupts to error detection. This is especially true since the same interrupt request is shared at the device level between the two SPI modules and the two I2C modules (See Section 6)

To use the SPI DMA interface, the SPIINT0.DMAREQEN bit should be set to '1' and SPIINT0.RXINTEN should be set to '0'.

The SPI will generate an active high request pulse when it is time to service the transmit and receive buffers.

On the C672x device, this request is routed to the dMAX unit:

- SPI0 request is routed to dMAX Event Input 13

- SPI1 request is routed to dMAX Event Input 14

**Note:** Remember, only a single DMA request is generated, and this should trigger a read of SPIBUF followed by a write to SPIDAT0 or SPIDAT1 through dMAX configuration.

# Appendix A

#### **SPI Registers** A.1

#### A.1.1 Introduction

Table A-1 lists the memory-mapped registers for the serial peripheral interface (SPI). See the device-specific data manual for the memory address of these registers.

|              |              | 10         | ible A-1. SFI Keyisters      |                                                                                       |

|--------------|--------------|------------|------------------------------|---------------------------------------------------------------------------------------|

| SPI0 Address | SPI1 Address | Mnemonic   | Name                         | Description                                                                           |

| 0x4700 0000  | 0x4800 0000  | SPIGCR0    | Global Control Register 0    | Contains the Software Reset bit for the Module                                        |

| 0x4700 0004  | 0x4800 0004  | SPIGCR1    | Global Control Register 1    | Controls Basic configurations of the module                                           |

| 0x4700 0008  | 0x4800 0008  | SPIINT0    | Interrupt Register           | Enable bits for interrupts, error, DMA and other functionality                        |

| 0x4700 000C  | 0x4800 000C  | SPILVL     | Interrupt Level Register     | SPI Interrupt Levels are set in this register                                         |

| 0x4700 0010  | 0x4800 0010  | SPIFLG     | Interrupt Flag Register      | Shows the status of several events during the operation                               |

| 0x4700 0014  | 0x4800 0014  | SPIPC0     | Pin Control Register 0       | Determines if pins will operate as general I/O or SPI functional pin                  |

| 0x4700 0018  | 0x4800 0018  | SPIPC1     | Pin Control Register 1       | Controls the direction of data on the I/O pins                                        |

| 0x4700 001C  | 0x4800 001C  | SPIPC2     | Pin Control Register 2       | Reflects the values on the I/O pins                                                   |

| 0x4700 0020  | 0x4800 0020  | SPIPC3     | Pin Control Register 3       | Controls the values sent to the I/O pins                                              |

| 0x4700 0024  | 0x4800 0024  | SPIPC4     | Pin Control Register 4       | Sets data values in the SPIPC3 register                                               |

| 0x4700 0028  | 0x4800 0028  | SPIPC5     | Pin Control Register 5       | Clears values in the SPIPC3 register                                                  |

| 0x4700 002C  | 0x4800 002C  | reserved   | Reserved                     | Reserved - Do not write to this register                                              |

| 0x4700 0030  | 0x4800 0030  | reserved   | Reserved                     | Reserved - Do not write to this register                                              |

| 0x4700 0034  | 0x4800 0034  | reserved   | Reserved                     | Reserved - Do not write to this register                                              |

| 0x4700 0038  | 0x4800 0038  | SPIDAT0    | Shift Register 0             | Main shift register                                                                   |

| 0x4700 003C  | 0x4800 003C  | SPIDAT1    | Shift Register 1             | Shift register used in automatic slave chip select mode only                          |

| 0x4700 0040  | 0x4800 0040  | SPIBUF     | Buffer Register              | Holds received word                                                                   |

| 0x4700 0044  | 0x4800 0044  | SPIEMU     | Emulation Register           | Mirror of SPIBUF. Read does not clear flags                                           |

| 0x4700 0048  | 0x4800 0048  | SPIDELAY   | Delay Register               | Sets SPIx_SCS mode, SPIx_SCS<br>pre-/post-transfer delay time and SPIx_ENA<br>timeout |

| 0x4700 004C  | 0x4800 004C  | SPIDEF     | Default chip select register | In SPIx_SCS decoded mode only: sets high<br>low/active SPIx_SCS signals               |

| 0x4700 0050  | 0x4800 0050  | SPIFMT0    | Format 0 register            | Configuration of data word format 0                                                   |

| 0x4700 0054  | 0x4800 0054  | SPIFMT1    | Format 1 register            | Configuration of data word format 1                                                   |

| 0x4700 0058  | 0x4800 0058  | SPIFMT2    | Format 2 register            | Configuration of data word format 2                                                   |

| 0x4700 005C  | 0x4800 005C  | SPIFMT3    | Format 3 register            | Configuration of data word format 3                                                   |

| 0x4700 0060  | 0x4800 0060  | TGINTVECT0 | TG interrupt vector          | Transfer group interrupt vector for line SPI INT0                                     |

| 0x4700 0064  | 0x4800 0064  | TGINTVECT1 | TG interrupt vector          | Transfer group interrupt vector for line SPI INT1                                     |

#### Table A-1. SPI Registers

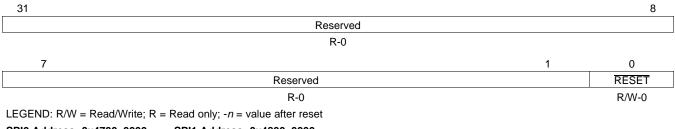

# A.1.2 SPI Global Control Register 0 (SPIGCR0)

The SPI global control register 0 (SPIGCR0) is shown in Figure A-1 and described in Table A-2.

# Figure A-1. SPI Global Control Register 0 (SPIGCR0)

SPI0 Address: 0x4700\_0000 SPI1 Address: 0x4800\_0000

#### Table A-2. SPI Global Control Register 0 (SPIGCR0) Field Descriptions

| Bit  | Field    | Value | Description                                                                                                 |

|------|----------|-------|-------------------------------------------------------------------------------------------------------------|

| 31-1 | Reserved |       | Reads return 0 and writes have no effect.                                                                   |

| 0    | RESET    |       | Software reset. This bit should be written to a '1' before any other operations are done on the SPI module. |

|      |          | 0     | SPI is held in a software reset.                                                                            |

|      |          | 1     | SPI is released from software reset.                                                                        |

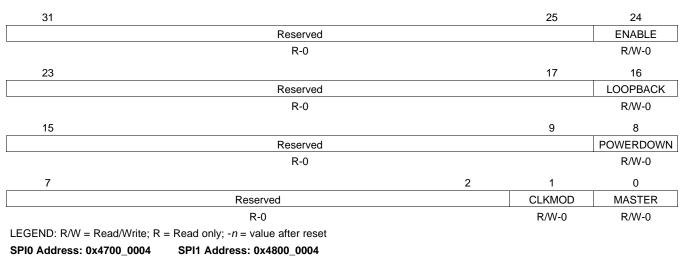

# A.1.3 SPI Global Control Register 1 (SPIGCR1)

The SPI global control register 1 (SPIGCR1) is shown in Figure A-2 and described in Table A-3.

# Figure A-2. SPI Global Control Register 1 (SPIGCR1)

#### Table A-3. SPI Global Control Register 1 (SPIGCR1) Field Descriptions

| Bit   | Field     | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|-----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-25 | Reserved  |       | Reads return 0 and writes have no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 24    | ENABLE    |       | SPI Enable. By default, the SPI is disabled after the software reset bit (SPIGCR0.RESET) is released . The other SPI configuration registers should be setup before writing a '1' to this bit. This will prevent the SPI from responding to bus operations erroneously while it is in the process of being configured. In particular, the SPIFLG.RXINTFLAG and SPIFLG.OVRNINTFLG bits are forced to 0 and the SPIx_CLK pin will not clock until this bit is set.                                                                                                                                                                                                               |

|       |           | 0     | SPI is disabled, and can be safely reconfigured                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       |           | 1     | SPI is enabled and will respond to bus transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 23-17 | Reserved  |       | Reads return 0 and writes have no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 16    | LOOPBACK  |       | Internal loop-back test mode. The internal self-test option can be enabled by setting this bit. If the SPIx_SIMO and SPIx_SOMI pins are configured with SPI functionality, then the SPIx_SIMO pin is internally connected to the SPIx_SOMI pin. The transmit data is looped back as receive data and is stored in the receive field of the concerned buffer.<br>Externally, during loop-back operation, the SPIx_CLK pin outputs an inactive value and SPIx_SOMI remains in high-impedance state. The SPI has to be initialized in master mode before the loop-back can be selected. If the SPI is initialized in slave mode or a data transfer is ongoing, errors may result. |

|       |           | 0     | Internal loop-back test mode disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       |           | 1     | Internal loop-back test mode enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 15-9  | Reserved  |       | Reads return 0 and writes have no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8     | POWERDOWN |       | SPI Powerdown mode is not supported on C672x devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       |           | 0     | SPI in active mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       |           | 1     | Illegal. Do not write a '1' to this bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7-2   | Reserved  |       | Reads return 0 and writes have no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Bit | Field   | Value | Description                                                                                                                                                                                                                                                                                                                |

|-----|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-0 | CLKMOD, |       | These two bits (CLKMOD, MASTER) determine whether the SPI operates in master or slave mode.                                                                                                                                                                                                                                |

|     | MASTER  | 00    | SLAVE MODE<br>SPIx_CLK is an input from the master who initiates the transfers.<br>Data is transmitted on the SPIx_SOMI pin and received on the SPIx_SIMO pin.<br>The <u>SPIx_SCS</u> pin is an input if configured as SPI slave chip select.<br>The <u>SPIx_ENA</u> pin is an output if configured as the SPI enable pin. |

|     |         | 11    | MASTER MODE<br>SPIx_CLK is an output and the SPI initiates transfers.<br>Data is transmitted on the SPIx_SIMO pin and received on the SPIx_SOMI pin.<br>The <u>SPIx_SCS</u> pin is an output if configured as SPI slave chip select.<br>The <u>SPIx_ENA</u> pin is an input if configured as the SPI enable pin.           |

|     |         | 01    | RESERVED - The SPI will not function properly with this setting                                                                                                                                                                                                                                                            |

|     |         | 10    | RESERVED - The SPI will not function properly with this setting                                                                                                                                                                                                                                                            |

# Table A-3. SPI Global Control Register 1 (SPIGCR1) Field Descriptions (continued)

# A.1.4 SPI Interrupt register (SPIINT0)

The SPI interrupt register (SPIINT0) is shown in Figure A-3 and described in Table A-4.

## Figure A-3. SPI Interrupt register (SPIINT0)

| Bit   | Field        | Value | Description                                                                                                                                    |

|-------|--------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-15 | Reserved     |       | Reads return 0 and writes have no effect.                                                                                                      |

| 24    | ENABLE HIGHZ |       | Selects between push pull and open drain modes for the SPIx_ENA pin in functional mode.                                                        |

|       |              | 0     | SPIx_ENA pin is driven when both active and inactive (push pull)                                                                               |

|       |              | 1     | SPIx_ENA pin is 3-stated when inactive and driven low when active (open drain)                                                                 |

| 23-17 | Reserved     |       | Reads return 0 and writes have no effect.                                                                                                      |

| 16    | DMAREQEN     |       | DMA request enable. Enables the DMA request signal to be generated for both receive and transmit channels.                                     |

|       |              | 0     | DMA is not used                                                                                                                                |

|       |              | 1     | DMA is used                                                                                                                                    |

| 15-9  | Reserved     |       | Reads return 0 and writes have no effect.                                                                                                      |

| 8     | RXINTEN      |       | Receive interrupt enable. An interrupt is to be generated when the SPIFLG.RXINTFLAG is set.                                                    |

|       |              | 0     | Interrupt will not be generated                                                                                                                |

|       |              | 1     | Interrupt will be generated                                                                                                                    |

| 7     | Reserved     |       | Reads return 0 and writes have no effect.                                                                                                      |

| 6     | OVRNINTEN    |       | Overrun interrupt enable. An interrupt is to be generated when the SPIFLG.RCVR OVRN is set.                                                    |

|       |              | 0     | Overrun interrupt will not be generated                                                                                                        |

|       |              | 1     | Overrun interrupt will be generated                                                                                                            |

| 5     | Reserved     |       | Reserved                                                                                                                                       |

| 4     | BITERRENA    |       | Enables interrupt on bit error.                                                                                                                |

|       |              | 0     | No interrupt asserted upon bit error.                                                                                                          |

|       |              | 1     | Enables an interrupt on a bit error                                                                                                            |

| 3     | DESYNCENA    |       | Enables interrupt on desynchronized slave. The desynchronization monitor is active in master mode for the 4-pin with enable and 5-pin options. |

|       |              | 0     | No interrupt asserted upon desynchronization error.                                                                                            |

|       |              | 1     | Enables an interrupt on desynchronization of the slave                                                                                         |

| Bit | Field      | Value | Description                                              |  |  |  |

|-----|------------|-------|----------------------------------------------------------|--|--|--|

| 2   | PARERRENA  |       | Parity Interrupt is not supported on C672x DSPs.         |  |  |  |

|     |            | 0     | Always write a '0' to this bit.                          |  |  |  |

|     |            | 1     | Illegal. Do not write a '1' to this bit.                 |  |  |  |

| 1   | TIMEOUTENA |       | Enables interrupt on SPIx_ENA signal timeout.            |  |  |  |

|     |            | 0     | No interrupt asserted upon SPIx_ENA signal timeout.      |  |  |  |

|     |            | 1     | Enables an interrupt on a timeout of the SPIx_ENA signal |  |  |  |

| 0   | Reserved   |       | Reads return 0 and writes have no effect.                |  |  |  |

#### Table A-4. SPI Interrupt register (SPIINT0) Field Descriptions (continued)

#### CAUTION

In 5-pin mode, the SPIx\_ENA pin must be configured for open drain mode and requires an external pullup resistor. See Section 2.6.

#### CAUTION

As described in Section 6 it is STRONGLY RECOMMENDED to use the DMA mode for data transfers and reserve interrupts for error conditions for the C672x SPI implementation. This means leaving the RXINTEN bit of this register at '0' and setting the DMAREQEN bit of this register to '1'.

# A.1.5 SPI Interrupt Level Register (SPILVL)

The SPI interrupt level register (SPILVL) is shown in Figure A-4 and described in Table A-5.

# Figure A-4. SPI Interrupt Level Register (SPILVL)

#### Table A-5. SPI Interrupt Level Register (SPILVL) Field Descriptions

| Bit  | Field      | Value | Description                                                                          |

|------|------------|-------|--------------------------------------------------------------------------------------|

| 31-9 | Reserved   |       | Reads return 0 and writes have no effect.                                            |

| 8    | RXINTLVL   |       | Receive interrupt level.                                                             |

|      |            | 0     | Receive interrupt is mapped to interrupt line INT0.                                  |

|      |            | 1     | Receive interrupt is mapped to interrupt line INT1.                                  |

| 7    | Reserved   |       | Reads return 0 and writes have no effect.                                            |

| 6    | OVRNINTLVL |       | Receive Overrun interrupt level.                                                     |

|      |            | 0     | Receive Overrun interrupt is mapped to interrupt line INT0.                          |

|      |            | 1     | Receive Overrun interrupt is mapped to interrupt line INT1.                          |

| 5    | Reserved   |       | Reads return 0 and writes have no effect.                                            |

| 4    | BITERRLVL  |       | Bit error interrupt level.                                                           |

|      |            | 0     | Bit error interrupt is mapped to interrupt line INT0.                                |

|      |            | 1     | Bit error interrupt is mapped to interrupt line INT1.                                |

| 3    | DESYNCLVL  |       | Desynchronized slave interrupt level. DESYNCLVL is used in master mode only.         |

|      |            | 0     | An interrupt due to desynchronization of the slave is mapped to interrupt line INT0. |

|      |            | 1     | An interrupt due to desynchronization of the slave is mapped to interrupt line INT1. |

| 2    | Reserved   |       | Reserved. Always write a '0' to this bit.                                            |

| 1    | TIMEOUTLVL |       | SPIx_ENA signal timeout interrupt level.                                             |

|      |            | 0     | An interrupt on a timeout of the SPIx_ENA signal is mapped to interrupt line INT0.   |

|      |            | 1     | An interrupt on a timeout of the SPIX_ENA signal is mapped to interrupt line INT1.   |

| 0    | Reserved   |       | Reads return 0 and writes have no effect.                                            |

#### CAUTION

In most cases, it is recommended to only use interrupt level 0 on a C672x device. This is because both SPI interrupt levels are combined again outside the SPI to assert the same CPU interrupt request. So making use of both interrupt levels inside the SPI will simply create additional overhead when servicing the SPI interrupt. For additional explanation, see Section 6.

# A.1.6 SPI Flag Register (SPIFLG)